# University of Piraeus - Department of Informatics Postgraduate Studies «Advanced Information Systems»

## **Master Thesis**

| Thesis            | Development of a soft error vulnerability analysis |  |

|-------------------|----------------------------------------------------|--|

|                   | framework for FPGA devices                         |  |

| Students Name     | Dimitrios Agiakatsikas                             |  |

| Fathers           | Sarantos                                           |  |

| Number of Records | MPSP/10064                                         |  |

| Supervisor        | Mihalis Psarakis, Assistant Professor              |  |

Delivery Date **10 / 2013**

## Committee

(signature) (signature) (signature)

M.Psarakis A.Pikrakis P.Kotzanikolaou Assistant Professor Lecturer Lecturer

#### **Abstract**

As the features sizes of the FPGA devices are moving aggressively to the nanometer regime, the singleevent upsets (SEUs) are expected to become a major reliability concern for the SRAM-based FPGAs. Given the limited information provided by the FPGA vendors about the susceptibility of the FPGA designs to soft errors, the research community requires SEU analysis tools to accommodate the development and assessment of SEU mitigation approaches. On the other hand, open-source CAD tools, such as RapidSmith [1] and Torc [2], have been recently proposed that target industrial FPGA architectures without escaping the boundaries of proprietary issues in contrast with the traditional opensource FPGA CAD tools. In this thesis, an open-source framework is presented for the soft error vulnerability analysis of Xilinx FPGA devices. The proposed framework will allow researchers to evaluate their reliability-aware CAD algorithms and estimate the soft error susceptibility of the designs at early stages of the implementation flow for the latest Xilinx architectures. Furthermore the well-known simulated-annealing placement algorithm is implemented in RapidSmith - where a limited random placer is currently supported - in order to evaluate the proposed post-placement sensitivity analysis method. To demonstrate the vulnerability analysis framework, a rich set of experiments is carried out. The thesis compares the soft error awareness of different packing/mapping tools (VTR and Xilinx tools) and different place tools (simulated annealing and Xilinx placers). The proposed method is evaluated by correlating its sensitivity analysis results with the Xilinx sensitivity report.

## Περίληψη

Καθώς το μέγεθος των χαρακτηριστικών των FPGA κινείται επιθετικά στην περιοχή των νανομέτρων, τα μεμονωμένα σφάλματα αναμένονται να γίνουν μείζον ανησυχία για την αξιοπιστία των SRAM FPGA. Λόγω των περιορισμένων πληροφοριών που παρέχουν οι κατασκευαστές των FPGA για την ευπάθεια των FPGA κυκλωμάτων σε παροδικά σφάλματα, η ακαδημαϊκή κοινότητα απαιτεί εργαλεία ανάλυσης των SEU, ώστε να αναπτυχθούν τεχνικές μετρίασης τους. Από την άλλη, πρόσφατα έχουν προταθεί εργαλεία CAD ανοιχτού λογισμικού, όπως το RapidSmith [1] και το Torc [2] που σε αντίθεση με κλασσικά εργαλεία CAD ανοιχτού λογισμικού, υποστηρίζουν πραγματικά FPGA χωρίς όμως να παραβιάζουν τα πνευματικά δικαιώματα των κατασκευαστών. Στην εργασία αυτή παρουσιάζουμε ένα πακέτο εργαλείων ανοιχτού κώδικα για την ανάλυση της ευπάθειας των Xilinx FPGA σε παροδικά σφάλματα. Το προτεινόμενο πακέτο εργαλείων θα επιτρέψει στους ερευνητές να αξιολογούν τους SEU αλγόριθμους αξιοπιστίας και να εκτιμούν την ευπάθεια των κυκλωμάτων σε παροδικά σφάλματα σε πρώιμα στάδια της υλοποίησης τους για τις πιο πρόσφατες αρχιτεκτονικές της Xilinx. Επίσης έχει αναπτυχθεί ο simulated-annealing αλγόριθμος τοποθέτησης στο περιβάλλον του Rapidsmith, όπου παρείχε μόνο ένα τοποθετητή τυχαίας επιλογής, ώστε να αξιολογηθεί η προτεινόμενη μέθοδος ανάλυσης της ευαισθησίας του κυκλώματος μετά την τοποθέτηση του. Για τη επίδειξη του πακέτου ανάλυσης της ευαισθησίας των κυκλωμάτων έχουν εκτελεστεί μία πλούσια πληθώρα πειραμάτων. Η εργασία συγκρίνει το πόσο προσεκτικά είναι διάφορα εργαλεία packing/mapping (VTR και εργαλεία της Xilinx) και διάφοροι τοποθετητές (simulated annealing και Xilinx τοποθετητές) στα παροδικά σφάλματα. Τα αποτελέσματα της ευαισθησίας από την προτεινόμενη μέθοδο έχουν αξιολογηθεί, συσχετίζοντας τα με τα αποτελέσματα από την αναφορά της ευαισθησίας από την Xilinx.

## **Acknowledgments**

I would like to express my gratitude to the persons who helped me through the realization of this thesis. First and foremost, I wish to thank my advisor professor Mihalis Psarakis, for his constant support, enthusiasm, patience and insights. He helped me come up with the thesis topic and guide me for almost a year of development. I would not be able to implement this framework and write this dissertation without his support. It was an honor for me to collaborate with such a brilliant person and scientist. I also own special thanks to Aitzan Sari, PhD candidate of my advisor. He passionately helped through the process of this framework. We spent together lot of days and nights implementing this framework. I will not forget the night he fell asleep while we were talking on skype and implanting the framework for hours. It was so funny. I will always be thankful to my best friends Dr.Grigorios Koulouras, who was my advisor back in the bachelor studies and Kyriakos Kontakos. Throughout these years, they have taught me topics of the cutting-edge technologies used in the embedded systems world. My sincere thanks goes to my bachelor fellow student Evangelos Tasoulas, who is one of my best friends and always supports me in the Linux environments. He is a guru in his field and I wish him to excel in his PhD at the University of Oslo. I also thank my friend Tasos Vereses, another Linux guru who always helps me in Linux topics. I thank Dr.Christos Evangelidis, Dr.Nikolaos Melis, Dr.Ioannis Kalogeras, professor Constantinos Nomicos and especially professor Nikolaos Thomaidis. They do not stop to support me and give me the most helpful advices for winning a place in the academic community. I also thank my current work, Geodynamics Institute of the National Observatory of Athens for its economic support while I was conducting this research. Last but not least, I would like to thank my dad, mom and little sister. My family has always been with me when I needed them, providing me emotional and economic support. I love them so much.

# **Table of Contents**

| 1 | Introduc        | tion                                            | 10 |

|---|-----------------|-------------------------------------------------|----|

|   | 1.1 Moti        | ivation                                         | 10 |

|   |                 | erved soft-errors failures in space missions    |    |

|   | 1.3 Thes        | sis Structure                                   | 12 |

| 2 | Backgro         | und and literature                              | 13 |

|   | 2.2 Wha         | at is an FPGA                                   | 13 |

|   | 2.3 FPG         | A Architecture                                  |    |

|   | 2.3.1           | Basic Logic Element (BLE)                       | 14 |

|   | 2.3.2           | Logic Block (LB)                                | 16 |

|   | 2.3.3           | Programmable Routing                            |    |

|   | <b>2.4 FPG</b>  | A Design Automation                             | 17 |

|   | 2.4.1           | Synthesis                                       |    |

|   | 2.4.2           | Packing and Mapping.                            |    |

|   | 2.4.3           | Placement                                       | 18 |

|   | 2.4.4           | Routing                                         | 21 |

|   | 2.4.5           | Bitstream generation                            |    |

|   | 2.5 The         | Rapidsmith framework                            |    |

|   | 2.5.1           | The XDL file                                    |    |

|   | 2.5.2           | XDL Syntax                                      |    |

|   | 2.5.3           | XDLRC Files                                     |    |

|   |                 | ted Work                                        |    |

| 3 | Methodo         | ology                                           | 29 |

|   | 3.1 Soft-       | error vulnerability analysis framework          | 29 |

|   | 3.2 Estin       | mation of sensitive configuration bits          | 31 |

|   | 3.2.1           | Sensitive Block Configuration Bits              | 31 |

|   | 3.2.2           | Sensitive Interconnection Configuration Bits    | 31 |

|   | 3.3 Post        | -placement analysis                             | 33 |

|   | 3.4 Post        | -routing analysis                               | 33 |

|   | <b>3.5</b> Soft | error vulnerability analysis framework packages | 34 |

|   | 3.5.1           | Placer Package                                  | 35 |

|   | 3.5.2           | Utilities package                               | 39 |

|   | 3.5.3           | Analysis package                                | 41 |

|   | 3.5.4           | UserInterface Package                           | 49 |

| 1 | Experim         | ental results                                   | 51 |

| 5 | Conclusi        | ons and Future Work                             | 57 |

| 6 | Bibliogra       | aphy                                            | 58 |

# **List of Figures**

| Figure 1 - Cost vs. Volume.                                                                     | 13 |

|-------------------------------------------------------------------------------------------------|----|

| Figure 2 – FPGA architecture.                                                                   | 14 |

| Figure 3 - Look Up Table (LUT).                                                                 | 15 |

| Figure 4 - Structure of basic BLE and LB [28].                                                  | 15 |

| Figure 5 - Routing Resources.                                                                   | 16 |

| Figure 6 - FPGA CAD flow                                                                        | 17 |

| Figure 7 - Bounding Box                                                                         | 19 |

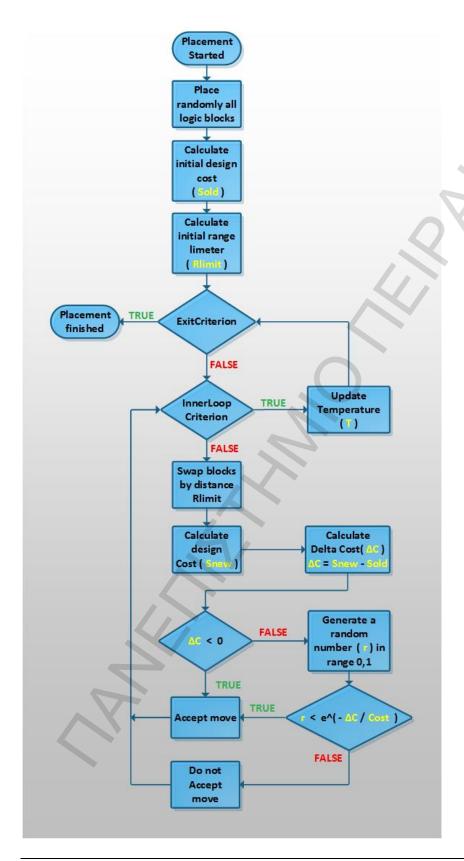

| Figure 8 - Adaptive Simulated Annealing                                                         | 20 |

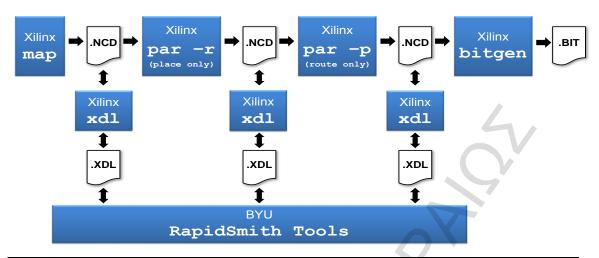

| Figure 9 - Block diagram of where XDL fits in the CAD flow [9]                                  | 22 |

| Figure 10 - XDL design statement example                                                        |    |

| Figure 11 - Unplaced instances in the XDL file.                                                 | 23 |

| Figure 12 -Placed instances in the XDL file.                                                    |    |

| Figure 13 - Unrouted nets in the XDL file.                                                      | 24 |

| Figure 14 - Routed nets in the XDL file.                                                        | 25 |

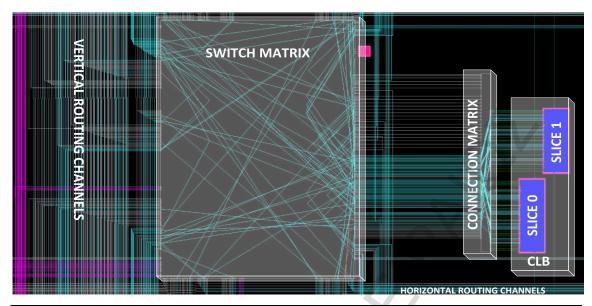

| Figure 15 - Xilinx general architecture                                                         | 26 |

| Figure 16 - XDLRC tile declaration                                                              | 26 |

| Figure 17 - XDLRC primitive site declaration                                                    | 26 |

| Figure 18 - XDLRC wire declaration                                                              | 27 |

| Figure 19 - XDLRC PIP declaration                                                               | 27 |

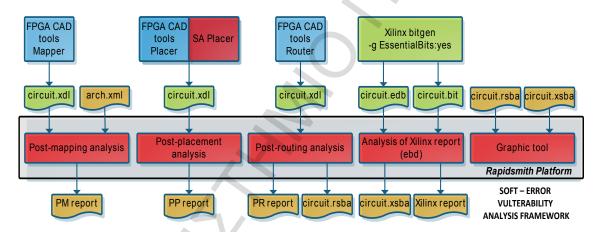

| Figure 20 - Soft error vulnerability analysis framework.                                        | 30 |

| Figure 21 - Sensitive bits of an interconnection block.                                         | 32 |

| Figure 22 - Short sensitive bits of two nets.                                                   | 33 |

| Figure 23 - Pseudo-code for the calculation of short & antenna-sensitive bits                   |    |

| Figure 24 - Unipi packages                                                                      | 34 |

| Figure 25 - Provided packages from the framework                                                | 35 |

| Figure 26 - Hierarchy of the classes within the placer package                                  | 35 |

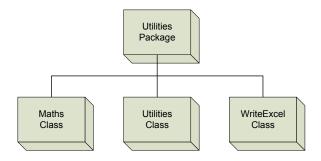

| Figure 27 - Hierarchy of the classes within the utilities package.                              | 39 |

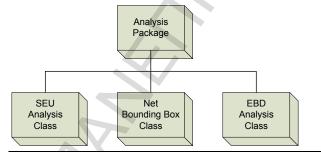

| Figure 28 - Hierarchy of the classes within the analysis package                                | 41 |

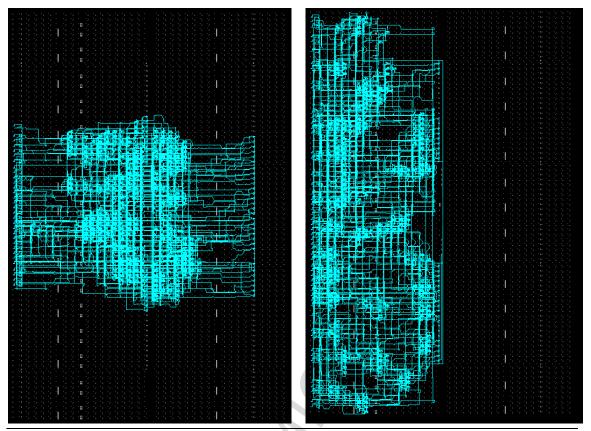

| Figure 29 - Placement with SA and Xilinx: Left: SA placer, Right: ISE placer.                   | 56 |

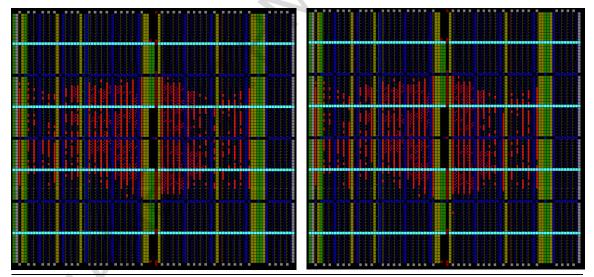

| Figure 30 - Visualization of the sensitive bits: Left: Proposed framework, Right: Xilinx report | 56 |

# **List of Tables**

| Table I - Black-box estimation of sensitive bits per block.                                       | .31  |

|---------------------------------------------------------------------------------------------------|------|

| Table II - QUIP benchmarks                                                                        | .52  |

| Table V - Placement performance: SA placer vs Xilinx ISE placer                                   | .52  |

| Table III - Post-mapping analysis(block configuration bits) using the Xilinx ISE flow [46]        | .53  |

| Table IV - Post-mapping analysis(block configuration bits) using the VTR [41], [40]               | .53  |

| Table VI - Post-placement analysis (interconnection configuration bits): SA placer vs. ISE placer | 54   |

| Table VII - Post-routing analysis (interconnection configuration bits): SA placer vs. ISE placer  | . 54 |

| Table VIII - Sensitive block configuration bits: Proposed framework vs. Xilinx report             | .55  |

| Table IX - Sensitive interconnection configuration bits: Proposed framework vs. Xilinx report     | .55  |

#### 1 Introduction

#### 1.1 Motivation

Over the last two decades, the research community has made significant efforts trying to find fault tolerant techniques in order to keep Field Programmable Gate Arrays (FPGAs) operational in high radiation environments. Such hostile environments can be found in space e.g. avionics in spacecraft, high-energy physics experiments e.g. CERN and many others. Although FPGA vendors provide high availability and reliability devices, using them in mission-critical applications [1] (i.e. can cause an environmental catastrophe or affect a human life) is a big challenge, due to their susceptibility to softerrors [2][3]. The designers not only have to develop qualified critical systems, but also have to keep the design cost low, forcing them to use commercial-off-the-shelf (COTS) FPGAs combined with emerging failure systems. FPGA vendors have introduced radiation-hardened devices (e.g. antifuse-based) to solve this problem. However, these devices are much more expensive less technologically developed than COTS FPGAs. For example an Airbus 380 has more than 700 antifuse-based FPGAs [4] (Actel SX-A family). The cost of 700 Actel SX-A FPGAs (if we consider that they have used the biggest FPGA in SX-A family, i.e. A54SX72A) is about 157000 US dollars (2013). If indeed, they used Xilinx COTS FPGAs with almost equal specifications (Virtex4 xc4vlx15) the cost would be almost the half, i.e. 84000 US dollars (2013).

Soft-errors have been a meaningful matter of the research community, since spacecraft electronics were affected from radiation in the early 1975s [5]. Spacecraft and airplane electronic systems have a variety of analog and digital components sensitive to radiation, making Single Event Upsets (SEUs) a major concern. SEUs are caused when charged particles (heavy ions and protons) hit a silicon atom transferring enough energy to produce a failure in the system. The amount of energy and the location of the strike in the device can cause transient or permanent errors. An SEU can produce transient soft errors in the combinational logic components, which can possibly be captured from Flip-Flops(FFs). Moreover, transient soft errors can directly affect the FFs of the FPGA and its hard block resources, such as RAM. Permanent failures are divided to hard errors or recoverable errors. Hard errors occur when charged particles bring on a lutch-up producing a short-cut between source and drain in mosfet technology that is commonly used in FPGA architectures. In case of recoverable errors, the configuration bitstream remains erroneous until it is downloaded again to the FPGA. These tradeoffs are a major problem in FPGA technology due to their high reliance on SRAM memory to store the configuration data [6].

Although, many fault tolerant techniques have been developed the last years, high reliability solutions are still a big challenge for the academic and industry research. FPGA vendors provide high capacity and performance devices while keeping the power consumption low. In order to develop FPGAs with these specifications, programmable logic industry uses silicon nanometer technologies and low operating voltages. However, shrinking of circuit dimensions to nanometer regime or shrinking noise margins [7], has revealed the susceptibility of the FPGA devices to emerging failure mechanisms raising several reliability issues [13]. Therefore, given that the feature sizes of the future beyond nanometer technologies will continue to shrink and the packaging cannot effectively shield the devices against SEUs [8], the implications caused by soft errors are expected to deteriorate drawing the attention of more researchers and practitioners from both domains of fault-tolerant computing and FPGA design automation. For the development and assessment of SEU mitigation methodologies and SEU-aware CAD tools for FPGAs, the research community needs the existence of soft error analysis tools able to measure the vulnerability of the designs and provide useful insights.

Recently, the research community provided open-source CAD tools that support commercial complex FPGA devices [9][10]. Motivated by this work, this thesis aims to provide a collection of open-source tools for the vulnerability analysis of Xilinx FPGA devices. The proposed framework will benefit the upcoming research providing valuable feedback to SEU mitigation approaches about the sensitivity of

\_

<sup>&</sup>lt;sup>1</sup> Configuration bits are categorized into *sensitive* and *non-sensitive* bits depending on the impact of soft errors to the circuit behavior [16], [47]. When a soft error in a configuration bit affects the circuit operation the bit is classified as sensitive (or essential according to Xilinx terminology) for the particular implementation, otherwise as non-sensitive. The actual failure rate of an FPGA design depends on the number of sensitive configuration bits or in other words the dynamic cross section of the design.

the FGPA configuration bits or the criticality of the design modules. For example, a TMR methodology could take advantage of the criticality analysis to reduce the area overhead by applying selectively the redundancy technique to the design modules [11]. Moreover, being able to estimate the soft error susceptibility of the design at various stages of the FPGA implementation flow, the proposed framework could be used for the development of SEU-aware PaR algorithms.

Several approaches have analyzed in the past the vulnerability of SRAM-based FPGAs into soft errors. These approaches are based either on fault injection experiments [6], [12], [13], [14], [15] or analytical methods [6], [16], [17], [18] to measure the sensitive configuration bits. The experimental approaches inject soft errors in the configuration bitstream of the design under test and, hence, they cannot apply during the FPGA design flow in order to provide an early sensitivity estimation. On the other hand, most research groups that have proposed analytical methods have developed proprietary vulnerability analysis tools targeting specific FPGA architectures which cannot be easily reproduced for another FPGA family. Furthermore, recent approaches have proposed SEU-aware placement and routing algorithms [8], [18], [19], [20], [21] in order to reduce the dynamic cross section of the FPGA designs. However, almost all these approaches have been demonstrated on the commonly used, academic VPR tool targeting virtual FPGA architectures. The proposed framework will enable the evaluation of such reliability-aware algorithms for off-the-shelf FPGA devices. The soft error vulnerability analysis framework is based on the recently proposed FPGA CAD platform, RapidSmith [9]. RapidSmith is a set of tools and APIs written in Java that manipulates a Xilinx human readable file format (XDL) and enables researchers to develop tools for the packing, placement, and routing of FPGA designs and parse/export configuration bitstreams. The proposed framework:

- evaluates the vulnerability of FPGA designs to soft errors analyzing the sensitivity of the configuration bitstreams. It classifies the sensitive bits according to their configuration type: block configuration bits (CLBs, IOBs, DSPs, etc.) and interconnection configuration bits.

- estimates the vulnerability of FPGA designs to soft errors at early phases of the FPGA implementation flow. In particular, it supports post-mapping analysis of the sensitive block configuration bits, post-placement analysis of the sensitive interconnection bits and final (post-routing) analysis of the total sensitive configuration bits. For the estimation of the sensitive configuration bits, the following methods are combined: theoretical analysis of the structure of Xilinx Virtex-5 programmable resources, analytical methods previously proposed in the literature [6], [18] for the estimation of sensitive interconnection bits and extraction of related information from the Xilinx sensitivity analysis results <sup>2</sup>.

- visualizes the sensitive configuration bits in the FPGA physical layout taking advantage of RapidSmith APIs. The sensitivity bitmap of the proposed method is compared with the sensitivity bitmap of Xilinx analysis.

#### 1.2 Observed soft-errors failures in space missions

Before continuing with the rest of this thesis it is worth to describe some observed failures in spacecraft electronic systems caused by cosmic radiation [22]. Back in 1989 Galileo mission was launched on a planetary exploration mission to Jupiter. All its electronic parts were fully tested and were radiation hardened with system-level redundancy and error detection capabilities. Despite the soft-errors mitigation techniques, safe holds failures where observed on some analog switches which fortunately did not have impact on the mission. These failures were believed to be due to SEUs. Another failure was experienced at the TOPEX/Poseidon mission, launched on August 1992. Proton radiation affected some 4N49 optocouplers of vendor Texas Instruments causing failures on some status signals and the circuits of the thruster command. On December 4, 1996, Cassini mission was lunched. Instead of a mechanical tape recorder they used a solid state recorder (SSR) constructed with high density RAM. Despite the single-bit correction and double-bit correction circuits it had, SSR experienced single-bit errors. On October 24, 1998, Deep Space 1 mission was lunched. A SEU caused failure in a FPGA due to a latch-up, while the recovery time of the system required 28 minutes which was an unexpected long time. Furthermore, on

\_

<sup>&</sup>lt;sup>2</sup> FPGA vendors provide utilities for the sensitivity analysis of the configuration bitstream. The Xilinx tool generates a map file (.ebd for essential bit description) for the characterization of the essential (sensitive) bits of the configuration bitstream. However, since it is not feasible to decode the raw bitstream data due to proprietary issues these sensitivity analysis results cannot provide an in-depth sensitivity analysis of the circuit.

April 24, 2001, Odyssey mission went into safe mode after 2 weeks in space due to failures in RAM, caused by a cosmic ray ion.

As FPGAs become more dencer and more powerful, they offer to the designers the integration of high-availability systems with hard real-time performance into a FPGA, such as avionics in airplanes and spaceships or medical systems. This raises need of new inventions from the academic and industrial research community to provide more robust SEU mitigation solutions that meet system reliability goals [23].

#### 1.3 Thesis Structure

The remainder of this master thesis is organized as follows. In chapter 2 the related work and literature is collected giving a better understanding in chapter 3, where information about the implemented soft-error vulnerability framework is provided. In more detail, chapter 3 gives an explanation of the methods used to evaluate the soft-error estimation tools. Furthermore, a description of the framework packages is provided. Experimental results are presented in chapter 4, and last come the conclusions of this master thesis.

## 2 Background and literature

This chapter contains the background information about the fundaments of modern FPGA architectures, the state-of-the-art CAD technology used in nowadays FPGAs and finally the related work section that presents the mitigating soft-errors techniques for SRAM based FPGAs, proposed from the research community.

#### 2.2 What is an FPGA

Field is the key word for defying a Field Programmable Gate Array (FPGA). FPGAs are Intergraded Circuits (ICs) that can be programmed in the field after manufacture. This means that FPGAs vendors must have some pre-fabricated digital circuity in the chip, enabling it to implement any given digital function from the user, simply by being appropriately programmed.

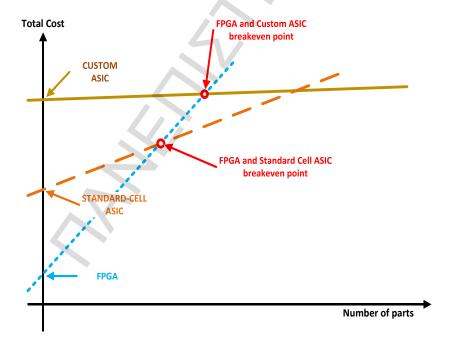

As described in [24], FPGAs are semiconductor devices that are based around a matrix of configurable logic blocks or Cluster of Logic Blocks (CLBs), connected via programmable interconnects (illustrated in Figure 2). FPGAs can be programmed to desired application or functionality requirements after manufacturing. This feature distinguishes from Application-specific integrated circuits (ASICs), which are custom manufactured for specific design tasks. Although One-Time Programmable (OTP) FPGAs are available, the dominant types are Static Random Access Memory (SRAM) based which can be re-programmed as the design evolves.

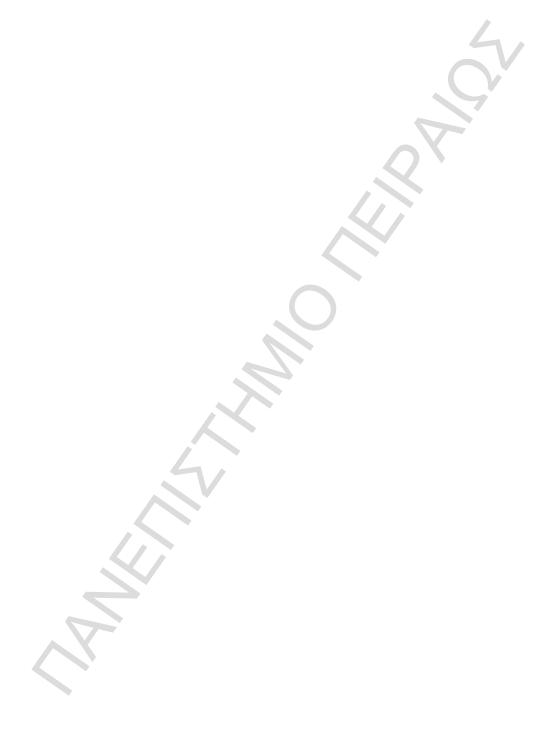

This innovative idea of a FPGA that would reduce the manufacturing time and cost of an IC from months to hours was introduced back in 1986 [25]. As a result, FPGAs are very popular these days, since faster design of complex products can be achieved, in contrast with ASICs. Because FPGAs are software configured, modifying a design is very fast, less risky and can be made in some hours, rather than months that is required for ASIC prototypes to be manufactured. FPGAs provide lower non-recurring engineering (NRE) costs, faster time to market and no expensive penalties at the verification phase [26] than ASICs. FPGAs are suitable for rapid prototype design, specialized digital systems (i.e. reconfigurable designs, System-On-Chip (SOC) designs) and low-volume IC production. Custom ASIC design is commonly used for high volume production, while Standard-Cell ASIC design for middle-volume production. Figure 1 illustrates the total cost as a function of IC parts of a design implemented in a FPGA, a Standard-Cell ASIC and custom ASIC device.

Figure 1 - Cost vs. Volume.

#### 2.3 FPGA Architecture

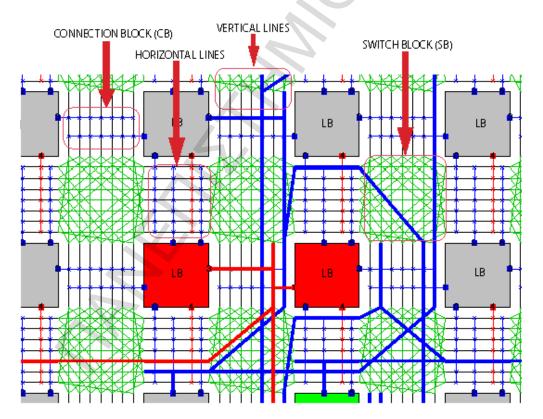

Traditionally, an FPGA can be composed of three fundamental elements depicted in Figure 2:

- The Logic Blocks (LBs), named as CLBs in Xilinx terminology. The LBs contain a group of Block Logic Elements (BLEs) named as Slices in Xilinx terminology, which implement combinational and sequential logic.

- The Input-Output Blocks (IOBs).

- The Programmable Routing, which is a matrix of wires that interconnect the LBs and the IOBs via Connection Blocks/Boxes (CBs) and Switch Blocks/Boxes (SBs). More detail is provided in the programmable routing section.

Commercial FPGAs also include extra memory, multipliers, memory controllers, high speed IOBs, Digital signal processing (DSP), Phase Locked Loops (PLLs), clock management, even embedded processors. These special blocks are referred in literature as hard blocks giving more logic utilization and speed at a FPGA.

Figure 2 - FPGA architecture.

#### 2.3.1 Basic Logic Element (BLE)

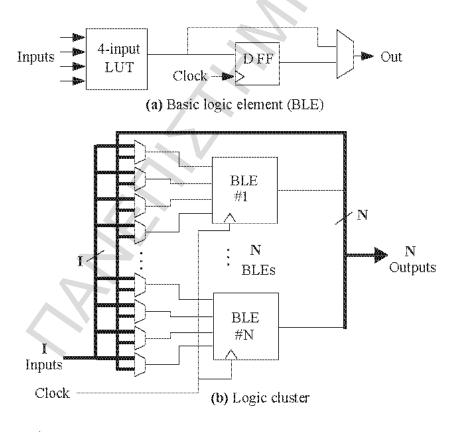

The BLE is built from the following components depicted in Figure 4:

- A Look-Up Table (LUT) to implement combinational logic.

- A Flip-Flop (FF) providing sequential behavior.

- A multiplexer for bypassing the FF if only combinational logic is needed.

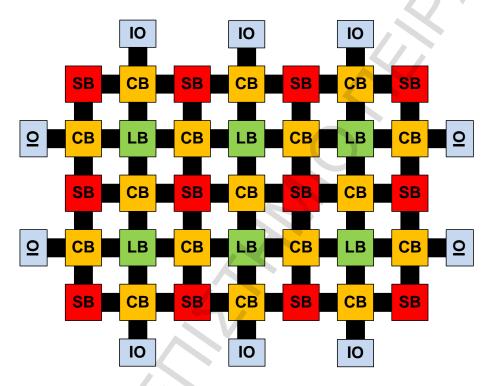

Figure 3 depicts the LUT which is the well-known truth table from digital design. A K-input LUT is typically composed from  $2^k$  SRAM that holds the configuration memory (LUT-mask) and K-1 multiplexers implemented as a tree to select the bit from SRAM and pass it to the LUT output. To simplify, we give an example of a LUT (illustrated in Figure 4) which can implement any combinational function of 4-inputs (A, B, C, D). It has a 4-inputs, 16bit SRAM ( $2^4 = 16bit$ ) and 15 x 2:1 multiplexers. Programming the LUT-MASK with the appropriate bit will assemble the desired function [27].

Figure 3 - Look Up Table (LUT).

Figure 4 - Structure of basic BLE and LB [28].

#### 2.3.2 Logic Block (LB)

Typically, commercial FPGAs have groups/clusters of BLEs that contain LUTs and FFs. Each LE has size N, while it consists of N interconnected BLEs as shown in Figure 4. Furthermore, a LB has *I* external pins that are passed via multiplexers to the BLEs inputs. In addition, the multiplexers provide the flexibility of interconnecting the BLEs in the same block/cluster. The *N* output pins of the LB are connected to the routing resources via the CBs.

## 2.3.3 Programmable Routing

Figure 5 depicts the routing resources. As high resource utilization and need for high bandwidth is necessary in FPGA designs, the routing resources occupy the largest area of silicon in a FPGA. The routing resources are constructed by three fundamental components [29].

- Switch Blocks/Boxes (SBs): SB is a hub that programmable connects horizontal and vertical metal lines of the routing channels. This is done via Programmable Interconnection Points (PIPs). Its flexibility depends on the property *Fs*, which defines the number of connection wiring segments it can handle.

- Connection Blocks/Boxes (CBs): CB is a switch in between the LB and the SB. It is responsible to connect the input and output pins of the LB with the routing wires of the SB. It has a property *Fc* describing the number of wires a LB pin can handle.

- Routing channels: Routing channels are horizontal and vertical metal wires that span between LBs, IOBs and Hard Blocks. In order to route the design, the appropriate PIPs must be programmed to interconnect the pins of the LBs, IOBs and Hard Blocks with the available metal wires. The amount of wires in a routing channel is referred in literature as size/width and is represented with the letter *W*.

Figure 5 - Routing Resources.

## 2.4 FPGA Design Automation

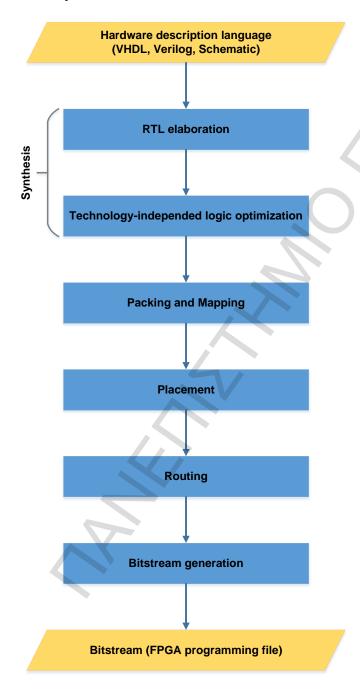

Implementing a circuit in a modern FPGA is a big challenge, requiring millions of configuration bits to be set on proper state, high or low. Although in 1960s, IC designs were hand-drawn, nowadays the complexity of FPGA architectures clearly prohibits those design procedures. Indeed, circuits are described in higher abstraction languages referenced as hardware description languages (e.g. Verilog and VHDL) and then converted from CAD tools into FPGA configuration bitstreams, which specify the state of every bit in the FPGA in order to assemble the described circuit. A way to keep the complexity of this problem low is to break it into some sub-problems. In the following sections a description of the sequential stages (depicted in Figure 6) that are involved in the procedure of mapping a circuit into a FPGA is presented.

Figure 6 - FPGA CAD flow.

#### 2.4.1 Synthesis

The synthesis procedure is a very complex task. In this stage the synthesis tool performs two steps. First, it converts the hardware description language into a neltlist of gates and second converts the neltlist of gates into a netlist of FPGA logic blocks, while trying to optimize the area and performance of the design. In more detail, the synthesis tool executes the following two sub-stages:

- RTL elaboration. This converts the hardware description language into gates, implementing datapath operations (such as additions and multiplications) and control logic (such as a set of finite-state machines or Boolean networks). It must be mentioned that in this sub-stage the synthesizer recognizes functions that can be handled by hard blocks (e.g. DSP) in the FPGA and forwards them to the packing and mapping stage. These functions are referenced as black-boxes.

- Technology-independed logic optimization. This optimizes both datapath and control logic, independed of the targeting FPGA architecture. There is a rich set of optimization techniques, which are performed in this sub-stage, such as removing redundant logic or sharing resources, don't care based optimization and many others.

## 2.4.2 Packing and Mapping

In this stage the packer packs several LUTs and Flip flops into one LB, respecting the targeting architectural limitations, such as the maximum number of LUTs and FFs the LB may contain and its available inputs and outputs. Afterwards, the packed instances of the design are technology mapped into the available LBs and also the black box functions into the available FPGA hard blocks. The optimization goals in this stage are to pack each LB to its maximum capacity, therefore maximize the FPGA resource utilization and also attempt to minimize the inputs and outputs signals of the LB, in order to route effectively the design in the routing stage.

#### 2.4.3 Placement

As described in [30], placement algorithms determine which logic block within an FPGA should implement each of the logic blocks required by the circuit. The optimization goals are to place connected logic blocks close together to minimize the required wiring (wire-length-driven-placement), and sometimes to place blocks to balance the wiring density across the FPGA (routability-driven-placement) or to minimize circuit speed (timing-driven placement).

In literature there are four different categories of placement methods for FPGA CAD tools [31]:

- simulated annealing

- min-cut

- quadratic

- parallel

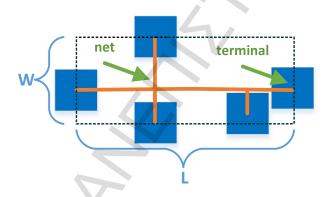

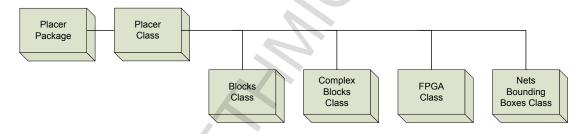

This thesis will focus on the well-known simulated annealing (SA) placement algorithm with adaptive schedule [30][32], as it is implemented it in the Rapidsmith framework, in order to replace the uncompleted placer package provided by Rapidsmith and evaluate the proposed SEU vulnerability framework. The main reason this algorithm has been chosen, is that its cost function can be easily modified from researchers to implement an SEU-aware placement algorithm [8], [18], [20]. SA placers mimic the natural process of a metal to be easily shaped in high temperatures while local improvement of the shape can be made as its temperature decreases. A linear congestion cost function is determined to calculate the quality of the placement. A wire-length cost function  $\bf C$  is selected to be used, which is the summary of all nets costs of a design. The cost of a net is the half perimeter of the bounding box (Figure 7) that encapsulates all the attached logic blocks to the net and is given from the following equation:

$$N_{cost} = q(i) * \left(\frac{bb_x(i)}{c_{av,x}(i)^{\beta}} + \frac{bb_y(i)}{c_{av,y}(i)^{\beta}}\right) (1)$$

where  $\mathbf{q}(\mathbf{i})$  is a constant value ranging from 1 for a net with less than 3 terminals, to its maximum value 2.73 for more than 50 terminals. The  $\mathbf{c}_{av,x}$  and  $\mathbf{c}_{av,y}$  are the average horizontal and vertical routing tracks respectively, trying to minimize the routing congestions of overloaded switch matrixes. The exponent  $\boldsymbol{\beta}$

has default value 1 and allows the relative cost of using narrow and wide routing channels to be adjusted. When giving a larger value to  $\beta$  parameter, more wiring in narrow channels is penalized. Setting  $\beta$  to zero reverts the linear congestion cost function to standard bounding box cost function, forcing to a more shrinked placement. In general the SA algorithm tries to swap random LBs in the FPGA pre-fabricated circuitry and accepts the swap if the design cost decreases. This would eventually produce a high quality placement. The SA algorithm executes the following steps:

- An initial placement (without taking in account the design cost) of the netlist logic blocks (LBs) is performed, assigning all LBs to the available and compatible resources in the FPGA fabric.

- The initial parameters of the SA algorithm are calculated. These include temperature **T** that controls the probability of accepting a random swap, **m** which is the number of swaps that will be executed in every temperature and finally **Rlimit** which determines how close must be the LBs for swapping. This leads to a procedure where random LBs for swap are selected from the entire area of the FPGA and as the temperature decreases only close LBs are selected for swapping.

- A large number of swaps are then made to gradually improve the placement quality. At high temperatures almost all swaps are accepted and as the temperature drops the acceptance probability decreases.

- The placement algorithm terminates when the temperature drops under a threshold.

In more details, the algorithm consists of two nested loops as depicted in Figure 8. The inner loop is executed m times and swaps two random LBs in the **Rlimit** area at every step. A swap is accepted when cost C is decreased. However, there is chance to accept the move, even if cost C is increased. This probability is computed by the equation  $\mathbf{r} < \mathbf{e}^{-\frac{\Delta C}{T}}$ , where  $\Delta C = C_{new} - C_{old}$  and  $\mathbf{r}$  is a random number ranging from 0 to 1. This feature gives the ability to escape local minima. The outer loop updates T, m and the **Rlimit** parameters. Finally the placement terminates when  $T < \epsilon * \frac{C}{N_{nets}}$ , where  $\epsilon$  is a constant ranging from 0.005 to 0.05 and  $N_{nets}$  is the amount of nets contained in the design.

The proposed SA placer supports the movement of all programmable resources, (e.g. logic slices, DSP slices, IOBs, BRAMs) but it is not capable to handle carry chains. Thus, someone should use either benchmarks without carry chains or the proposed SA placer will not move the tiles that contain instances with curry chains.

Figure 7 - Bounding Box

Figure 8 - Adaptive Simulated Annealing

#### 2.4.4 Routing

In the previous stage the placer tried to choose the correct LB locations to place the instances with the aim that the router would need less effort to route the design. The router enables the required programmable interconnection points (PIPs) in order to connect effectively all LB input and output pins described in the design. Designed to be able to route successfully a design, a CAD flow must have an equal skillful placer and router. If the routing algorithm has excellent performance while the placement algorithm does not, it is obvious that the routing will fail and vice versa. Sometimes the placement and routing is performed simultaneously, as the cost of a design in the placement procedure is inherently weak at addressing both wirability and timing optimizations [33].

In general the routing architecture is represented as a directed graph. Each pin and wire of the design becomes a node and each potential connection an edge. The router algorithm has to find and connect all the nodes in the routing resource graph. There are two main router algorithms in the FPGA CAD technology. The routability-driven that try to find the shortest path and the time-driven which use more complex algorithms, giving priority mostly to the critical paths of the design.

#### 2.4.5 Bitstream generation

The bitstream generation is the conversion of a routed design file into a sequence of bits, called bitstream. The bitstream is uploaded to the FPGA in order to configure every bit state in it. This will eventually produce the actual hardware.

#### 2.5 The Rapidsmith framework

Rapidsmith is a set of APIs written in Java that read, manipulate and write the Xilinx human readable file format (XDL), whereas hiding syntactic details from the user. Rapidsmith gives the ability to researchers to try out new ideas in all fields of FPGA CAD tools on Xilinx FPGAs. A design must be converted first in the appropriate XLD file format in order to be imported to Rapidsmith. Rapid development of packing, placement or routing tools and parse/export configuration bitstreams can be achieved taking the advantage of the available APIs provided by the framework. It is argued that Java is a slow and memory-hungry programming language, in contrast with native machine languages like C, but no speed or memory issues where observed, while developing the proposed soft error vulnerability tools. Java is a free object-oriented programming language with useful libraries for big data structures which makes it very powerful for developing CAD tools. The researchers can focus at their algorithms implementation, while time-consuming memory management is taken care from the Java garbage collector, cleaning up the unused objects without big performance tradeoffs. In order to develop a tool in Rapidsmith someone must understand the basic syntax of XDL files. Therefore, in the following sections a description of the the Xilinx XDL file structure will be provided, over some examples.

#### 2.5.1 The XDL file

Xilinx vendor provides the Xilinx Design Language (XDL) to interface and access the features of a design or a device. XDL has two main sides. One side is the description of the FPGA architecture, providing all the primitives and routing fabric of the FPGA. The other side is the description of the design. XDL is a human readable ASCII file, offering a representation of the proprietary Xilinx Netlist Circuit Description (NCD) file format in every CAD stage (i.e. mapped, placed or routed design). The user is free to insert or extract any desired information at different CAD stages of the Xilinx design flow. XDL can describe the following designs:

- A partially or full Mapped design.

- A partially or full Placed design.

- A partially or full Routed design.

Figure 9 - Block diagram of where XDL fits in the CAD flow [9].

#### 2.5.2 XDL Syntax

The XDL is a self a documented file format explaining every statement with an example comment. In order to understand the XDL syntax we will examine a design with two instances, while it is mapped, placed and routed.

#### **Design statement**

Every XDL file has a design statement which includes the name of the design, the part number of the FPGA and also a list with some attributes of the CAD tools. Below in Figure 10 we can see an example of the design statement with its attributes list. We observe that the name of the design is "lut" and the targeting FPGA is the xc5vlx110tff1136-1.

Figure 10 - XDL design statement example

#### **Instance statement**

An instance is represented in Rapidsmith with the design. Instance class. It always begins with the keyword "inst". An instance can be placed or unplaced in the FPGA layout. The configurations of the instance are provided by a string that starts with the keyword "cfg". It must be mentioned that the name of the instance must be unique in a design in order to avoid name conflicts in Rapidsmith. Figure 11 depicts an example with two instances in a mapped design. The name of the first instance is *out0\_OBUF*. The second instance is *out0\_* The two instances are not placed, while in the next CAD stage these instances have to be placed in a compatible Primitive site of *SLICEM* and *IOB* type, respectively.

```

inst "out0_OBUF" "SLICEM",unplaced ,

cfg " A5LUT::#OFF A5RAMMODE::#OFF A6LUT:LUT U0:#LUT:O6=(A1*(~A2*(~A3*(~A4*(~A5*~A6)))))

_BEL_PROP::A6LUT:BEL:A6LUT A6RAMMODE::#OFF ACY0::#OFF ADI1MUX::#OFF

AFF::#OFF AFFINIT::#OFF AFFMUX::#OFF AFFSR::#OFF AOUTMUX::#OFF AUSED::0

B5LUT::#OFF B5RAMMODE::#OFF B6LUT::#OFF B6RAMMODE::#OFF BCY0::#OFF

BDI1MUX::#OFF BFF::#OFF BFFINIT::#OFF BFFMUX::#OFF BFFSR::#OFF BOUTMUX::#OFF

BUSED::#OFF C5LUT::#OFF C5RAMMODE::#OFF C6LUT::#OFF C6RAMMODE::#OFF

CCY0::#OFF CDI1MUX::#OFF CEUSED::#OFF CFF::#OFF CFFINIT::#OFF CFFMUX::#OFF

CFFSR::#OFF CLKINV::#OFF COUTMUX::#OFF COUTUSED::#OFF CUSED::#OFF

D5LUT::#OFF D5RAMMODE::#OFF D6LUT::#OFF D6RAMMODE::#OFF DCY0::#OFF

DFF::#OFF DFFINIT::#OFF DFFMUX::#OFF DFFSR::#OFF DOUTMUX::#OFF DUSED::#OFF

PRECYINIT::#OFF REVUSED::#OFF SRUSED::#OFF SYNC_ATTR::#OFF WA7USED::#OFF

WA8USED::#OFF WEMUX::#OFF "

inst "out0" "IOB",unplaced,

cfg " DIFFI_INUSED::#OFF DIFF_TERM::#OFF IMUX::#OFF OUSED::0 PADOUTUSED::#OFF

PULLTYPE::#OFF TUSED::#OFF OUTBUF:out0_OBUF: PAD:out0:

DRIVE::12 OSTANDARD::LVCMOS33 SLEW::SLOW "

```

Figure 11 - Unplaced instances in the XDL file.

We continue with the same instances being placed. We observe that the instance *out0\_OBUF* is placed in the primitive site *SLICE\_X0Y0*, while the slice is located in the primitive tile *CLBLM\_X1Y0*. Furthermore, the instance *out0* is placed in the primitive site *LIOB\_X0Y1* which is located in the primitive tile *AP21*.

```

inst "out0_OBUF" "SLICEM",placed CLBLM_X1Y0 SLICE_X0Y0 ,

cfg " A5LUT::#OFF A5RAMMODE::#OFF A6LUT:LUT_U0:#LUT:O6=(A1*(~A2*(~A3*(~A4*(~A5*~A6)))))

_BEL_PROP::A6LUT:BEL:A6LUT A6RAMMODE::#OFF ACY0::#OFF ADI1MUX::#OFF

AFF::#OFF AFFINIT::#OFF AFFMUX::#OFF AFFSR::#OFF AOUTMUX::#OFF AUSED::0

```

```

B5LUT::#OFF B5RAMMODE::#OFF B6LUT::#OFF B6RAMMODE::#OFF BCY0::#OFF

BDI1MUX::#OFF BFF::#OFF BFFINIT::#OFF BFFMUX::#OFF BFFSR::#OFF BOUTMUX::#OFF

BUSED::#OFF C5LUT::#OFF C5RAMMODE::#OFF C6LUT::#OFF C6RAMMODE::#OFF

CCY0::#OFF CDI1MUX::#OFF CEUSED::#OFF CFF::#OFF CFFINIT::#OFF CFFMUX::#OFF

CFFSR::#OFF CLKINV::#OFF COUTMUX::#OFF COUTUSED::#OFF CUSED::#OFF

D5LUT::#OFF D5RAMMODE::#OFF D6LUT::#OFF D6RAMMODE::#OFF DCY0::#OFF

DFF::#OFF DFFINIT::#OFF DFFMUX::#OFF DFFSR::#OFF DOUTMUX::#OFF DUSED::#OFF

PRECYINIT::#OFF REVUSED::#OFF SRUSED::#OFF SYNC_ATTR::#OFF WA7USED::#OFF

WA8USED::#OFF WEMUX::#OFF "

inst "out0" "IOB",placed LIOB_X0Y1 AP21 ,

cfg " DIFFI_INUSED::#OFF DIFF_TERM::#OFF IMUX::#OFF OUSED::0 PADOUTUSED::#OFF

PULLTYPE::#OFF TUSED::#OFF OUTBUF:out0_OBUF: PAD:out0:

DRIVE::12 OSTANDARD::LVCMOS33 SLEW::SLOW"

```

Figure 12 -Placed instances in the XDL file.

#### Net statement

Moreover, in Figure 14 the above instances have been routed. The router tries to connect the outpins (sources) and the inpins (sinks) of the design primitive sites which are described with the net statement. The net statement is represented in Rapidsmith with the design. Net class. Nets have 3 different types: VCC, GND and WIRE. The keyword WIRE is the default type and is not required to be present in the XDL file. Nets are described with two components: The pins and the PIPs. The pips are only available when the design has been routed. As an example, Figure 13 depicts an unrouted net. Pins define the source and one or more sinks within the net. A pin is identified by the name of the instance it resides in and also with its internal name within the instance. Pips are represented with the design.PIP class in Rapidsmith and are used to connect the sources and sinks of the design using the prefabricated wires located in the matrixes. A PIP is uniquely described with the name of the tile that it resides followed with the internal coordinates that indicate the location of the PIP in the tile. Furthermore, a PIP has two wires with a connection between them. Figure 13 describes the unrouted net, while Figure 14 describes the same net, while it is routed. In the unrouted net example we can clearly see that the signal from output pin of instance 'out0\_OBUF' must be connected to the input pin of instance 'out0'. In the routed net example, PIPS are added to the XDL file to describe the connection of the sources and the sinks of the two instances. Almost all PIPS are unidirectional and are described with the symbol ("->"). In some cases someone can find some bidirectional PIPS ("-=") used with long lines, which route the global nets of the design. However, Rapidsmith does not use this description, avoiding problems that can be caused by the XDL conversion.

```

net "out0_OBUF" ,

outpin "out0_OBUF" A ,

inpin "out0" O ,

```

Figure 13 - Unrouted nets in the XDL file.

```

net "out0_OBUF",

outpin "out0_OBUF" A ,

inpin "out0" O ,

pip CLBLM_X1Y0 M_A -> SITE_LOGIC_OUTS12 ,

pip INT_X0Y0 WN2END_S0 -> NW2BEG2 ,

pip INT_X0Y1 NW2MID2 -> IMUX_B41 ,

pip INT_X1Y0 LOGIC_OUTS12 -> WN2BEG0 ,

pip IOI_X0Y1 IOI_IMUX_B41 -> IOI_O11 ,

pip IOI_X0Y1 IOI_O11 -> IOI_OPINWIRE1 , # __ROUTETHROUGH:D1:OQ

pip IOI_X0Y1 IOI_O_PINWIRE1 -> IOI_O1 ,

;

```

Figure 14 - Routed nets in the XDL file.

#### 2.5.3 XDLRC Files

XDLRC report files are generated by the Xilinx XDL command line tool, i.e. xdl –report –pips – all\_conns <partName>, describing the architecture of the corresponding FPGA device. The size of the generated files varies from some megabytes to some gigabytes for recent devices. Although there are only few different types of tiles in a Xilinx FPGA, the Xilinx resource descriptions files are gigantic and cannot be easily manipulated. The reason is that the same attributes for similar tiles is repeated in the XDLRC files. However, Rapidsmith uses a custom form of serialization and compression libraries to compress these files. For example the XDLRC report file of a Virtex 7 is compressed to 5965 KB form an initial size of 73.6GB.

In order to describe the XDLRC report files, the general architecture description of a Xilinx FPGA. Xilinx is recalled. FPGAs consist of an array of tiles. The most frequent tile found in a Xilinx FPGA is the Configurable Logic Block (CLB) and the interconnection blocks (connection matrix and switch matrix). The CLB consists of two slices containing the look-up-tables and the flip-flops implementing combinational or sequential logic. Every CLB has two interconnection tiles on its left side. The first interconnection tile is called connection matrix and the second switch matrix. The switch matrix is a tile with PIPS that connects the horizontal and vertical wires of the routing channels. The connection matrix is a tile which is responsible to connect the input and output pins of the slices (contained in the CLBs) with the routing lines of the switch matrix. Figure 15 depicts a CLB with its interconnections tiles. Besides CLBs and interconnection tiles Xilinx provides and other tile types, such as Random Access Memory (RAM) blocks, Phase-locked loops (PLLs), digital signal processors (DSPs), even high performance embedded processors, providing high performance and capacitance to the FPGA. For example Xilinx vendor provides the new Zynq-7000 family (2013), which embeds a state-of-the-art ARM Cortex A9 micro-processor core in it, enabling designers to evaluate high performance systems-on-chip (SoC), while keeping the power consumption low.

Figure 15 - Xilinx general architecture

In the next section the corresponding descriptions of tiles, primitive sites, wires and PIPS within the XDLRC report files is provided.

#### Tiles

Tiles are represented in Rapidsmith with the device. Tile class. A tile starts with the keyword "tile" followed by the X, Y coordinates that indicate the location of the tile in the FPGA layout. Furthermore, it contains the name of the tile and the number of the primitive sites that are hosted in it. The tile ends with a "tile summary", summarizing the name and type of the tile. The declaration finishes with some numbered statistics. Figure 16 depicts a tile which resides on the X = 1, Y = 14 coordinates of the FPGA fabric layout. It has a unique name  $CLB\_X6Y63$ , while its type is CLB. Finally the tile carries 4 primitive sites (CLB 4).

```

(tile_1 14 CLB_X6Y63 CLB 4

(tile_summary CLB_X6Y63 CLB 122 403 148)

```

#### Figure 16 - XDLRC tile declaration

## **Primitive sites**

Primitive sites are represented in Rapidsmith in the device.PrimitiveSite class. Furthermore, a primitive type enumeration is available in Rapidsmith. Only instances (design.Instance class) compatible to the primitive site type can be placed in it. Also a list with pinwires describing the name and direction of the pins contained in the site is provided in the XDLRC description file. In Figure 17 we depict an example of a primitive site declaration. From the attribute *SLICE\_X9Y127* we can notice that the site type is *SLICEL*. Any instance compatible to this type can reside on *SLICE\_X9Y127*. Finally, the description ends with a list containing the pins of the site, which are the BX, BY, CE input pins and the XMUX out pin with their corresponding internal tile names.

```

(primitive_site SLICE_X9Y127 SLICEL internal 27

(pinwire BX input BX_PINWIRE3)

(pinwire BY input BY_PINWIRE3)

(pinwire CE input CE_PINWIRE3)

(pinwire XMUX output XMUX_PINWIRE3)

```

Figure 17 - XDLRC primitive site declaration

#### Wire

A list of wires is declared in a tile that describes the routing resources which are used to connect the specific tile with other tiles. For example in Figure 18 the wire E2BEG0 is connecting the tile with 3 interconnection tiles (INT\_X8Y63, INT\_X9Y63, INT\_X9Y62) and two CLBs (CLB\_X7Y63, CLB\_X8Y63). The connections are denoted with the keyword 'conn' and are described with the tile name and the wire name used for the connection. Connections which are located in the connection matrix are not programmable (fixed), in contrast with connections in the switch matrixes that use PIPS for programmable connection. Wire enumeration is provided by the device. WireEnumerator class. The enumeration is represented with integers, giving significant compression to the XDLRC description file. Another technique evaluated in the Rapidsmith, in order to reuse wire data structures is the use of relative tile offsets.

```

(wire E2BEG0 5

(conn CLB_X7Y63 CLB_E2BEG0)

(conn INT_X8Y63 E2MID0)

(conn CLB_X8Y63 CLB_E2MID0)

(conn INT_X9Y63 E2END0)

(conn INT_X9Y62 E2END_S0)

```

Figure 18 - XDLRC wire declaration

#### PIP

As mentioned above, a PIP is responsible to connect two wires in a switch matrix. Figure 19 outlines a PIP declaration, which describes that the wire 'BEST\_LOGIC\_OUTSO' will be connected with the wire 'BYP INT B5', if the PIP is set high ("turned on") in the switch matrix INT X7Y63.

```

(pip INT_X7Y63 BEST_LOGIC_OUTS0 -> BYP_INT_B5)

```

Figure 19 - XDLRC PIP declaration

#### **Primitive Definitions**

At the end of the XDLRC report file there is a collection of primitive definitions for the targeting Xilinx FPGA part number, which are used for reference and are not very frequent used from Rapidsmith, as some necessary information is not provided from Xilinx vendor. Father information for the XDL file format can be found in [9][34].

#### 2.6 Related Work

Many previous approaches have analyzed the vulnerability of the configuration memory of SRAM-based FPGAs to soft errors and investigated their effects in the behavior of various applications. These approaches are based either on fault injection experiments [35], [12], [13], [14], [15] or analytical methods [6], [16], [17], [18].

The fault injection process is performed using either accelerated radiation testing [6], [12], [15] or fault injection tools [13], [14], [15]. In radiation-based approaches, the device under test is exposed to a controlled flux of radiation, emitted either by proton accelerators [12] or radioactive sources like proton beam [15] to slowly introduce upsets in the memory cells of the device. To reduce the high cost needed for the experimental setup of the radiation tests, fault injection approaches [13], [14], [15] emulate the effects of SEUs in the FPGA's configuration memory as bit-flips in the memory cells. The fault injection approaches can be used to analyze the susceptibility of the final configuration bitstream and thus they cannot apply during the FPGA design flow in order to provide an early estimation. To avoid the time-consuming fault simulations, several analytical approaches have been proposed [6], [16], [17], [18].

In [16] and [17] Asadi et al. present an analytical soft error rate estimation methodology which is based on the error propagation probability of the SEUs from the error sites to system outputs. In [18] the

authors propose methods for the estimation of the sensitive configuration bits after the placement process, which are adopted by our post-placement analysis method.

In [12] Johnson et al. have performed fault injection experiments on a Xilinx Virtex 1000 FPGA in order to compare the performance of simulation and accelerated radiation based tests. The simulator was built on the SLAACI-V PCI FPGA board. The board had tree Virtex 1000 FPGAs (PE0, PE1 and PE2). PE1 was used to emulate the effects of SEUs by changing the contains of the configurations memory throw partial reconfiguration, PE1 had the golden bitstream and the last PE2 FPGA was used to capture the output results of PE1 and PE2, which were operating identically under normal circumstances. To validate the simulation, acceleration test was used to slowly introduce upsets in the PE1 with proton beam. The output errors were captured with the same way in the simulation test, i.e. comparing the output of the PE1 and PE2 with the PE0 FPGA. The simulator predicted 97% of the output errors observed during the radiation tests.

Furthermore, in [6] Bellato et al. proposed an analytical method to investigate the effects of SEUs in the SRAM configuration memory of a Xilinx Virtex XCV300 FPGA and also introduced radiation fault injection experiments to validate the correctness of their results. In order to analyze the effects of SEUs on the FPGA resources, the authors first decoded the stored configuration memory in the device by continuously observing the generated bitstream outputs of all possible configuration modes of a single given resource. They accomplished to decode the 192 bits of the CLB resources and find out how they are affected from SEUs. A bit flip in a LUT could modify an implemented function, defected muxes could cause new exit paths from the CLB and last the initialization of the CLB could change the behavior of its internal components. The researchers categorized the possible interconnection soft-errors scenarios, by inserting or deleting nets in an initial design and afterwards observing the differences in the generated bitstreams. These scenarios are as follows:

- Open bit scenario: In order to emulate this scenario, they deleted a net that was connecting two

pins in the CLB. The PIP which was connecting the two pins was set to open state producing an

open-bit error.

- Short bit or bridge scenario: In order to emulate this scenario, they replaced an existing net with a new one, activating another PIP which connected an unknown logic value to the CLB.

- Input Antenna scenario: They inserted a new net starting from an unused input pin to a used output. The new input pin could influence the behavior of the CLB especially if it was connected at a high frequency output pin.

- Output Antenna scenario: They inserted a new net starting from a used input pin to an unused output. The new input pin did not influence the behavior of the CLB because the output pin was not used.

- Conflict scenario: A new net connected two used input and output pins, producing a conflict, since the unknown output values of the input pin were fed from the output pin.

- None scenario: They added a net in order to enable a PIP which connected two unused pins. This did not affect the functioning of the CLB.

Due to this analysis, they were able to understand the consequences of a soft error in the configuration memory and the programmable resources. However, the preliminary analysis has been done for a Virtex device and cannot be easily reproduced for other FPGA architectures. Recent approaches have proposed SEU-aware mapping, placement and routing algorithms [8],[18], [19], [20], [21] in order to reduce the vulnerability of the FPGA designs. In [8] and the [36] placement and routing algorithms of VPR tool are modified in order to reduce the susceptibility of the FPGA circuits to SEUs. In [19] the authors present a reliability-aware place and route algorithm to mitigate the effects of SEUs to TMR-based circuits. In [20] a modified version of the VPR algorithms is proposed to reduce the bridging faults caused by SEUs in the configuration memory. In [21] the proposed SEU-aware placement and routing algorithms incorporate both application level and physical level factors to reduce the soft error rate. Most of the above approaches have been demonstrated on the well-established academic VPR tool targeting only virtual FPGA architectures. The proposed framework will enable the evaluation of such reliability-aware algorithms for industrial FPGA devices.

## 3 Methodology

The methodology chapter will provide to the reader the description of the proposed soft-error vulnerability analysis framework, a deep analysis of the methods which are used to estimate the sensitive bits in placed and routed designs and finally a briefly analysis of the framework code structure that is implemented, as the proposed open-source framework (documented in Java-docs) and a technical report will be soon available on the internet.

## 3.1 Soft-error vulnerability analysis framework

The research community has intensively addressed the last years the problem of bridging the academic CAD tools with commercial CAD tools and therefore be able to apply them to real industrial FPGAs. For example, the authors in [37] connected an academic synthesis and verification tool (ABC) with the Xilinx's ISE CAD flow and compared it with the Xilinx Synthesis Technology (XST) tool. In [38], the JBits interface [39] was combined with the open-source VPR tool [32] to generate configuration bitstreams for Xilinx Virtex architectures (placed and routed by VPR) for the needs of a fault tolerant methodology. In more detail, the authors described the architecture of the Xilinx Virtex FPGAs and modified the source of the VPR tool in order to make it capable to place and route a design on a Virtex (XCV100, XCV300) FPGA. Finally, an interface was implemented to connect the Jbits interface for Virtex with the output of the VPR tool and therefore generate the bitstream configuration file. Recently, the authors in [40] developed an extension of the academic Verilog-To-Routing (VTR) [41] flow to synthesize, optimize and technology map a netlist with ODIN II [42] and ABC tools on a Virtex-6 Xilinx FPGA, pack and place it with the VPR tool and subsequently route and generate the bitstream with the Xilinx CAD flow. The drawback of these approaches is the extra effort needed to develop netlist models and interfaces to support new FPGA architectures, e.g. only a specific Virtex-6 device is supported in [40].

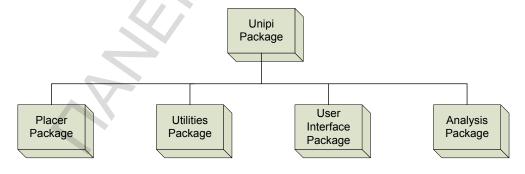

Motivated by the above approaches and the need of research community for FPGA reliability analysis tools, an open–source soft error vulnerability analysis framework based on RapidSmith [9] was developed, that is capable to target industrial FPGA architectures. RapidSmith is a set of open-source tools and APIs written in Java language that manipulate the Xilinx human readable XDL files, allowing researchers to try out new ideas in various fields of FPGA CAD domain. In order to be imported to RapidSmith, any design netlist must be first converted to the compatible XDL file format. Note that an XDL netlist can be easily exported in almost all implementation stages using Xilinx utilities. The advantage of RapidSmith compared to the traditional academic FPGA CAD flows is its ability to target the latest Xilinx FPGA architectures. This was the main reason that of using RapidSmith to build the vulnerability analysis tool. Figure 20 depicts the main functions supported by the proposed soft error vulnerability analysis framework. The sensitivity analysis of an FPGA design to soft errors can be performed at all stages of the FPGA design flow, while all different types of configuration bits, e.g. block configuration bits (CLBs, IOBs, DSPs, etc.) and interconnection configuration bits are considered. The user is free to run the entire flow and measure the dynamic cross section of the final FPGA design or run individual tools at earlier stages of the flow to pre-estimate the soft-error vulnerability of the design.

The functions supported by the framework are the following:

- Post—mapping analysis of the block configuration bits: It extracts the FPGA resource

utilization data (e.g. number of utilized slices, DSPs, IOBs, BRAMs, LUT inputs, slice

functional mode, I/O direction and attributes, etc.) from the XLD netlist produced by the

packing/mapping step and analyses the sensitivity of the block configurations bits based on

a precompiled resource usage profile (described in an xml file).

- Post–placement analysis of the interconnection configuration bits: It takes into consideration the actual sites of the used resources obtained by the placement process (extracted from the XDL netlist) and the goals of the routing algorithm and analyses the possibility of a net to become open-wired or short-wired with another net due to a soft error in a programmable interconnection point (PIP). So, it estimates the vulnerability of the interconnection configuration bits before the final routing. This tool is mainly based on sensitivity analysis methods previously proposed in the literature [6], [18].

Post-routing analysis of the interconnection configuration bits: It provides a more accurate

analysis since it relies on the final routed circuit. It considers all possible defects that can be

caused by a soft error in a programmable interconnection point, i.e. open faults, bridging

faults and antenna faults. The final analysis results are written in a text file (.rsba stands for

routing sensitive bit analysis) for further processing.

- Analysis of the Xilinx report for essential configuration bits: Xilinx supports the generation of an essential (sensitive) bitmap along with the generation of the configuration bitstream (using flag –g EssentialBits:Yes in the bitgen command). The tool analyses the Xilinx report and parses the sensitive bitmap (.ebd file) and the bitstream (.bit file) using RapidSmith packages. After that, it classifies the sensitive bits as reported by Xilinx into block, interface and interconnection configuration bits and allocates them to configuration frames. This sensitivity bitmap analysis could facilitate scrubbing-based SEU mitigation approaches to prioritize the testing of most critical configuration frames of the FPGA device in order to reduce the mean repair time [43]. The results are written in a text file (.xsba stands for Xilinx sensitive bit analysis) for further processing.

- Visualization of soft-error vulnerable areas: A Graphic tool built as extension of the Rapidsmith Device. Explorer class reads the results from the two previous analysis steps (.rsba and .xsba files) and illustrates the vulnerable areas of the FPGA layout. This allows the user to visualize the vulnerability analysis results of the proposed approach and compare them with the sensitivity report of Xilinx.

Figure 20 - Soft error vulnerability analysis framework.

Since the analysis tools require only the XDL description of the circuit under test, the framework can interact with any FPGA CAD tool (packer, mapper, placer, router) provided that the XDL circuit description is available. Also, given that RapidSmith can manipulate the XDL description of any FPGA device the proposed framework can support all existing Xilinx FPGA architectures. Currently, the tools have been tested for Virtex-5 and Virtex-6 families supporting all the available devices. The only restriction is that the analysis of Xilinx report (.ebd file) for Virtex-6 is not feasible due to undocumented internal frame structure from Xilinx. The .xml file provided to the post—mapping analysis tool includes the results of the usage profiling of the programmable resources for a specific FPGA architecture. According to this profile, each primitive resource has been mapped with its theoretical configuration bits based on its possible usage mode. The well-known Simulated Annealing (SA) placement algorithm is also implemented, described in [30] in order to replace the uncompleted placer package provided by RapidSmith framework and to evaluate the proposed analysis methods. The main reason, this algorithm

\_

$<sup>^{\</sup>rm 3}$  The graphic tool entirely implemented by Mr. Aitzan Sari.

<sup>&</sup>lt;sup>4</sup> The analysis and implementation of usage profiling was entirely evaluated by Mr. Aitzan Sari. He has performed the profiling of Virtex-5 and Virtex-6 architectures and he plans to integrate the profiles of more Xilinx architectures in the future.

was selected, is that its cost function can be easily modified from researchers to implement an SEU-aware placement algorithm [8], [18], [20].

## 3.2 Estimation of sensitive configuration bits

In this section a description of the methods used to estimate the sensitive configuration bits is provided. Both programmable logic resources and routing resources are considered in the analysis since both categories contribute significantly to the total amount of sensitive configuration bits as shown by the experimental results. The analysis distinguishes the sensitive bits to interconnection and block configuration bits while the sensitive interconnection bits are being further classified to open, short and antenna sensitive bits.

#### 3.2.1 Sensitive Block Configuration Bits

The estimation of sensitive block configuration bits can be applied as early as the mapping process on the FPGA design flow. The block configuration bits are classified into CLB, IOB, BRAM and DSP resource configuration bits estimation while two estimation methods are proposed: a black-box method and a structural analysis method. The former method depends only on the post-mapping resource utilization data while the latter uses a structural sensitivity analysis of the programmable resources to improve the estimation accuracy.

The black-box estimation approach [43] assumes that all configuration bits of a used programmable resource are sensitive. According to this pessimistic assumption, the number of sensitive bits per programmable resource can be extracted from the documented structure of configuration bitstream. The sensitive bits of programmable blocks  $\mathbf{R}$  are calculated by dividing the configuration bits of a column for block  $\mathbf{R}$  ColumnBits<sub>R</sub> to the number of blocks in the column ColumnBlocks<sub>R</sub> and multiplying with the number of blocks  $\mathbf{N}_{\mathbf{R}}$  used in the design.

Sensitive bits (R) =

$$\frac{\text{ColumnBits}_R}{\text{ColumnBlocks}_R} * N_R$$

(2)

For example, in the Virtex-5 family a CLB column needs 11 configuration frames (although it is documented that a CLB column requires 10 configuration frames, a careful CLB utilization and bitstream examination reveals that the actual number of frames is 11) and with 1280 bits per frame (excluding the ECC word since it is considered as non-sensitive) there are 14080 configuration bits which are uniformly distributed across the column. A CLB column in the Virtex-5 family consists of 20 CLBs and each CLB contains two slices. Applying Equation 2, gives 704 configuration bits per CLB or 352 configuration bits per slice. The sensitive configuration bits for all programmable resources are calculated similarly. Table I summarizes the results for the primary block resources of Virtex-5 architecture. The figure in parenthesis in the second column of Table I denotes the number of configuration frames per column, i.e. 30 configuration frames (28 block plus 2 interface frames) per IOB column, 4 configuration frames (2 block plus 2 interface frames) per BRAM column and 2 interface configuration frames per DSP column.

| Block (R) | $ColumnBits_R$ | ColumnBlocks <sub>R</sub> | Sensitive bits |

|-----------|----------------|---------------------------|----------------|

| CLB       | 14080 (11)     | 20                        | 704            |

| IOB       | 35840 (30)     | 40                        | 896            |

| BRAM      | 5120 (4)       | 4                         | 1280           |

| DSP       | 2560 (2)       | 8                         | 320            |

Table I - Black-box estimation of sensitive bits per block.

#### 3.2.2 Sensitive Interconnection Configuration Bits

The fault modeling and the vulnerability analysis of the FPGA routing resources have been studied extensively in the past [6], [13], [14], [18]. Here, the fault modeling of routing resources proposed by several previous approaches are adopted, according to which the routing faults due to soft errors in the programmable interconnection points can be open, short or antenna. So, an interconnection configuration bit is termed as open-sensitive when a soft error causes an open wire, as short-sensitive when it causes the

bridging of two distinct nets, and finally as antenna-sensitive when it results to a hanging wire connected to a net.

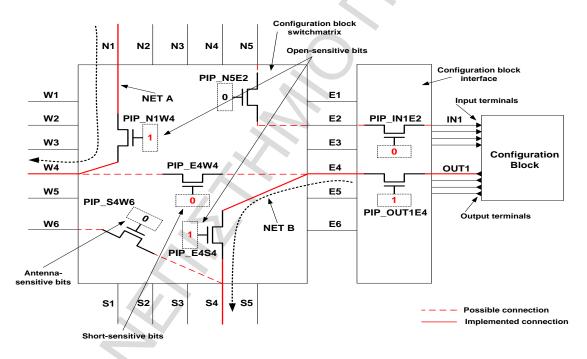

The estimation method is based on the simple interconnection block model depicted in Figure 21 which describes adequately the interconnection blocks of Virtex-5 and Virtex-6 FPGA architectures. The interconnection block consists of a switch-matrix and an interface block. The interface block is used to connect the terminals (inputs/outputs) of a resource block (CLBs, IOBs, etc.) to the switch matrix which in turn provides access to the global interconnection network.

Consider the nets connected to the interconnection block of Figure 21: two nets are routed through the switch matrix, namely *NET A* and *NET B* which use the wires *N1W4* and *E4S4*, respectively and the connections made for these wires are realized with a single PIP (Programmable Interconnection Point) for each net. As shown in the example, *NET B* is connected to the configurable block through the interface block. These PIPs are open-sensitive PIPs since a soft error will result in disconnecting the starting wire from the end wire of the switch matrix. A soft error, for example, in the SRAM cell of *PIP\_N1W4* will disconnect the *N1* wire of *NET A* from the *W4* wire.

Figure 21 depicts also a net-bridging scenario where two nets are shorted as a consequence of soft error in *PIP\_E4W4* which connects wires *E4* and *W4*. Since these wires are used by nets *A* and *B*, respectively, a short connection is formed between these two nets. In the case of antenna-sensitive bit, a soft error causes a wire used by a net to be connected to an unused wire of the switch matrix. For example, *PIP\_S4W6* is considered as antenna-sensitive bit, since an SEU will cause wire *S4* to be connected to *W6* producing a wire acting as antenna on *NET B*.

Figure 21 - Sensitive bits of an interconnection block.

Although in most cases an antenna will not lead to erroneous output, it will degrade the performance of a circuit, especially when it occurs in high-frequency nets such as a clock net. Finally, Figure 5 shows a non-sensitive PIP (*PIP\_N5E2*) where a soft error will not affect the circuit operation since the bridging wires are not used. The information required by the above analysis (e.g. which PIPs are in use, which wires can be connected through PIPs, etc.) is extracted from the XDL model of the circuit.

As described in the related work section, the framework provides two roadmaps for the analysis of the sensitive interconnection bits: the post-placement and the post-routing analysis. The post-placement analysis provides to the designer a vulnerability estimation early in the design flow while it can also drive a reliability aware placement algorithm [18], [20], [8]. On the other hand, the post-routing analysis provides a more precise calculation of the sensitive configuration bits.

## 3.3 Post-placement analysis

The proposed framework has adopted the method introduced in [18] to calculate the open-sensitive and short-sensitive bits of an FPGA design. The open-sensitive bits for a single net are calculated using the Manhattan distance applied on its Bounding Box (BB) assuming  $X_{min}Y_{min}$  and  $X_{max}Y_{max}$  being the coordinates of the BB. Equation 3 is used to calculate the number of open-sensitive bits. The post-placement method adopts the q [44] factor used also in the simulated annealing placement algorithm to characterize the pin-count of the particular net.

Sens. bits (open) =

$$(|X_{max}-X_{min}| + |Y_{max}-Y_{min}| + 1) * q$$

(3)

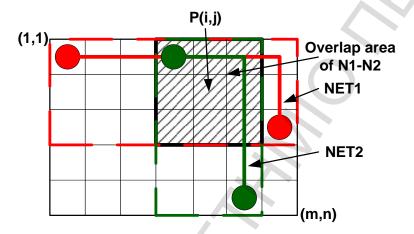

The method for the estimation of short-sensitive bits proposed in [18] is based on the usage probability of switch matrices within the BB of a net. To find the short-sensitive bits between two nets NET1 and NET2 the method just uses the product of their usage probabilities over the overlap area (Equation 4). A simple example is shown in Figure 22 where two nets have been considered to illustrate the estimation process.

Sens. bits (short)=

$$\sum_{\forall (i,j)in_{overlap_{area}}} p^{N1}(i,j)*p^{N2}(i,j)$$

(4)

where  $\mathbf{p}^{N}(\mathbf{i}, \mathbf{j})$  is the probability of net N routing through switch matrix  $(\mathbf{i}, \mathbf{j})$ . For more details the reader can refer to [18].

Figure 22 - Short sensitive bits of two nets.

## 3.4 Post-routing analysis