## Πανεπιστήμιο Πειραιώς – Τμήμα Πληροφορικής

# Πρόγραμμα Μεταπτυχιακών Σπουδών «Προηγμένα Συστήματα Πληροφορικής»

## Μεταπτυχιακή Διατριβή

| Τίτλος Διατριβής      | Αξιολόγηση της απόδοσης ετερογενών<br>επαναδιαμορφώσιμων πολυπύρηνων επεξεργαστών<br>Performance evaluation of heterogeneous reconfigurable<br>multicore processors |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ονοματεπώνυμο Φοιτητή | Παπανικολάου Ιωάννης                                                                                                                                                |

| Όνομα Πατρός          | Κοσμάς                                                                                                                                                              |

| Αριθμός Μητρώου       | ΜΠΣΠ 15065                                                                                                                                                          |

| Κατεύθυνση            | Προηγμένες τεχνολογίες ανάπτυξης λογισμικού                                                                                                                         |

| Επιβλέπων             | Ψαράκης Μιχαήλ, Επίκουρος Καθηγητής                                                                                                                                 |

Πανεπιστήμιο Πειραιώς-Τμήμα Πληροφορικής

Πρόγραμμα Μεταπτυχιακών Σπουδών στα

Προηγμένα Συστήματα Πληροφορικής

## Τριμελής Εξεταστική Επιτροπή

(υπογραφή) (υπογραφή) (υπογραφή)

Ψαράκης Μιχαήλ Αποστόλου Δημήτριος Κοτζανικολάου Παναγιώτης Επίκουρος Καθηγητής Αναπληρωτής Καθηγητής Επίκουρος Καθηγητής

## Περίληψη

Τα τελευταία χρόνια τα FPGA έχουν διεισδύσει στις αγορές και επιλέγονται όλο και περισσότερο από σχεδιαστές για την υλοποίηση πολυάριθμων εφαρμογών. Τα FPGA εξελίχθηκαν από εξειδικευμένα λογικά κυκλώματα που χρησιμοποιούνταν για την διασύνδεση πολλαπλών εμπορικών κυκλωμάτων, σε συσκευές με υψηλή πυκνότητα επαναπρογραμματιζόμενων λογικών πόρων πού είναι σε θέση να υλοποιήσουν σύνθετα συστήματα σε ένα ολοκληρωμένο κύκλωμα. Ένα από τα μεγαλύτερα πλεονεκτήματα των FPGA είναι η ευελιξία που προσφέρουν καθώς η λειτουργικότητα τους μπορεί να αλλάξει φορτώνοντας ένα νέο configuration file στην μνήμη τους. Επεκτείνοντας την ευελιξία των FPGA με την χρήση δυναμικής μερικής επαναδιαμόρφωσης (Dynamic Partial Reconfiguration) ο εκάστοτε σχεδιαστής έχει την δυνατότητα να επαναδιαμορφώσει περιοχές του FPGA χωρίς να επηρεάζει ολόκληρο το σύστημα. Η δυνατότητα αυτή επιτρέπει στα FPGA να προσαρμόζονται δυναμικά σε συγκεκριμένες προδιαγραφές.

Η παρούσα μεταπτυχιακή διατριβή παρουσιάζει και αξιολογεί μια αποτελεσματική αρχιτεκτονική ετερογενών επαναδιαμορφώσιμων πολυπύρηνων επεξεργαστών. Η αρχιτεκτονική χρησιμοποιεί δυναμική μερική επαναδιαμόρφωση για να προσαρμόσει τους διαθέσιμους πόρους σύμφωνα με τον φόρτο εργασίας. Η αποδοτικότητα επιτυγχάνεται βελτιστοποιώντας την χρήση των πόρων καθώς και την χρήση της ενέργειας παρέχοντας αρκετή υπολογιστική ισχύ έτσι ώστε το σύστημα να τηρεί τις προδιαγραφές. Η αρχιτεκτονική αυτή υλοποιήθηκε και αξιολογήθηκε στην αναπτυξιακή πλατφόρμα Zybo που διαθέτει το Xilinx Zynq-7000 FPGA. Τα αποτελέσματα αυτού του πειράματος καταδεικνύουν ότι με την χρήση της προτεινόμενης αρχιτεκτονικής είναι εφικτό να διατηρηθεί η επιθυμητή απόδοση μειώνοντας την χρήση της ενέργειας.

#### **Abstract**

Over the last few years, Field Programmable Gate Arrays have penetrated the markets and are increasingly embraced by designers for numerous applications. FPGAs evolved from small glue logic circuits to devices with high-density of reconfigurable logic resources that are capable of implementing large systems in a single chip. One great asset that FPGAs offer is high flexibility since their functionality can be altered by simply loading a new binary file in their configuration memory. Extending the flexibility, a unique capability of FPGAs called Dynamic Partial Reconfiguration (DPR) allows regions to be programmed with new functionality while applications are still running in the remainder of the device. Hence, making FPGAs able to adapt to specific constraints by modifying its hardware in real time.

This thesis demonstrates and evaluates an efficient architecture of a heterogeneous reconfigurable multicore system on a Xilinx MPSoC. The architecture utilizes DPR to adjust hardware resources according to the workload while the device is operating. Efficiency is achieved by optimizing both area and power usage while delivering high performance in order to meet strict time deadlines. The architecture is being implemented, evaluated and tested on a Zybo development board featuring a Xilinx Zynq-7000 FPGA. This system can load custom reconfigurable modules containing multiple instances of Xilinx's Intellectual Property softcore Microblaze to supplement the preexisting hardwired processor. The results of this experiment demonstrate that it is possible to maintain a desirable performance while decreasing power usage.

## Contents

| Περίληψη                                                 | 3    |

|----------------------------------------------------------|------|

| Abstract                                                 | 3    |

| 1 Introduction                                           | 7    |

| 1.1 Motivations and Objectives                           | 7    |

| 1.2 Thesis Outline                                       | 7    |

| 2 FPGA Overview                                          | 8    |

| 2.1 Introduction                                         | 8    |

| 2.1.1 FPGA Evolution through the Years                   | 8    |

| 2.1.2 Basic Components                                   | . 10 |

| 2.1.3 Uses and Application Fields                        | . 14 |

| 2.2 FPGA Development Flow                                | . 15 |

| 2.3 Partial Reconfiguration                              | . 19 |

| 2.3.1 Partial Reconfiguration Fundamentals               | . 21 |

| 2.3.2 Configuration Mechanisms                           | . 22 |

| 2.3.3 Floorplaning for Reconfigurable Designs            | . 22 |

| 2.3.4 Reconfigurable Families                            | . 22 |

| 2.3.5 Benefits of Partial Reconfiguration                | . 23 |

| 2.4 Processors on FPGAs                                  | . 26 |

| 2.4.1 Soft Processors                                    | . 26 |

| 2.5 Zynq-7000 Architecture                               | . 28 |

| 2.5.1 Processing System                                  | . 28 |

| 2.5.2 Programmable Logic                                 | . 30 |

| 2.5.3 Processing System — Programmable Logic Interfaces. | . 32 |

| 3 Heterogeneous Multicore Systems                                                                                                                                                                                                                                                                 | . 33                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 3.1 Multi-Processors System-on-Chip                                                                                                                                                                                                                                                               | . 33                                           |

| 3.1.1 Heterogeneous MPSoC Architecture                                                                                                                                                                                                                                                            | . 34                                           |

| 3.1.2 Homogeneous MPSoC Architecture                                                                                                                                                                                                                                                              | . 35                                           |

| 3.1.3 Hardware Accelerators                                                                                                                                                                                                                                                                       | . 36                                           |

| 3.2 Hardware Reconfiguration in MPSoCs                                                                                                                                                                                                                                                            | . 37                                           |

| 3.2.1 Runtime Adaptive MPSoC                                                                                                                                                                                                                                                                      | . 37                                           |

| 3.2.2 Benefits of the RAMPSoC Approach                                                                                                                                                                                                                                                            | . 38                                           |

| 3.3 MPSoCs Design Challenges                                                                                                                                                                                                                                                                      | . 39                                           |

| 3.3.1 Cache Coherence                                                                                                                                                                                                                                                                             | . 39                                           |

| 3.3.2 Power and Temperature                                                                                                                                                                                                                                                                       | . 39                                           |

| 3.3.3 Reliability Issues                                                                                                                                                                                                                                                                          | . 40                                           |

| 3.4 MPSoC Applications                                                                                                                                                                                                                                                                            | . 40                                           |

|                                                                                                                                                                                                                                                                                                   |                                                |

| 3.4.1 Applications Mapping                                                                                                                                                                                                                                                                        | . 40                                           |

| 3.4.1 Applications Mapping      4 Implementation of a Heterogeneous Reconfigurable Multicor                                                                                                                                                                                                       |                                                |

|                                                                                                                                                                                                                                                                                                   | e System 42                                    |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor                                                                                                                                                                                                                                       | re System 42<br>. 43                           |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture                                                                                                                                                                                                       | re System 42 . 43                              |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture                                                                                                                                                                                                       | re System 42 . 43 . 43                         |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture                                                                                                                                                                                                       | re System 42 . 43 . 43 . 44                    |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture  4.1.1 Building Blocks  4.1.2 Interfacing the Softcores to the Processing System  4.2 Hardware Development                                                                                            | re System 42 . 43 . 43 . 44 . 45               |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture                                                                                                                                                                                                       | re System 42 . 43 . 43 . 44 . 45 . 46          |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor  4.1 General System Architecture                                                                                                                                                                                                      | e System 42 . 43 . 43 . 44 . 45 . 46 . 48      |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture  4.1.1 Building Blocks  4.1.2 Interfacing the Softcores to the Processing System  4.2 Hardware Development  4.2.1 Design Entry  4.2.2 Hardware Synthesis and Implementation  4.3 Software Development | re System 42 . 43 . 43 . 44 . 45 . 46 . 48     |

| 4 Implementation of a Heterogeneous Reconfigurable Multicor 4.1 General System Architecture                                                                                                                                                                                                       | e System 42 . 43 . 43 . 44 . 45 . 46 . 48 . 50 |

| 5.2 Results                                   | 50 |

|-----------------------------------------------|----|

| 6 Conclusion and future work                  |    |

|                                               |    |

| Bibliography and references                   | 55 |

| Appendix A. Template applications source code | 57 |

| A1. ARM Processor                             | 57 |

| A2. Microblaze0 softcore                      | 64 |

| A3. Microblaze1 softcore                      | 65 |

#### 1 Introduction

## 1.1 Motivations and Objectives

The main motivation behind this thesis is to study the advanced FPGA design technique called Partial Reconfiguration and to highlight some of the strengths and the weaknesses of this technique. Starting from a concept we progress through all the design stages required reaching an intricate system which we test extensively. The objective is to utilize a low budget FPGA and with the help of Partial Reconfiguration to present a novel architecture that improves the performance of the system.

#### **1.2 Thesis Outline**

This thesis is composed of six chapters. The remainder of this thesis is summarized as follows:

Chapter 2 provides the needed background theory of the presented thesis work. The Xilinx FPGA architecture is introduced, by providing terminology and details of the different components. Partial Reconfiguration is also introduced in this chapter with an overview of its development flow, key concepts, and benefits. Finally, a description of the processors used in FPGAs and the Zynq-7000 architecture are presented, since both of them are concepts strongly used in many aspects of this thesis.

Chapter 3 is a literature review of the main branches of multicore systems. Starting with an introduction on MPSoCs, the heterogeneous and homogeneous architectures are presented. This chapter also presents the concept of hardware reconfiguration in MPSoCs along with a novel architecture proposed in a white paper. The chapter concludes with a discussion on MPSoC design challenges and a brief reference on MPSoC applications.

Chapter 4 describes the implementation of a heterogeneous reconfigurable multicore system, with a focus on its architecture as well as on its hardware and software development methodology.

Chapter 5 presents the experimental results from the deployment of the heterogeneous reconfigurable system on a Zybo Zynq MPSoC. The system was tested with multiple applications coming from various commercial backgrounds. Furthermore, the power consumption of the system is presented and compared against a static standalone system.

Chapter 6 evaluates the results and justifies the cases that the proposed architecture fulfills its purpose. Drawbacks and potential improvements are also discussed in this chapter as well as potential future work.

#### 2 FPGA Overview

Field programmable gate arrays or FPGAs are a special type of integrated circuits that can be programmed at the field after manufacture. This technology is used by system developers to design, debug, and implement unique hardware solutions without having to develop custom silicon devices. Vendors such as Xilinx and Altera are selling FPGA chips blank or unprogrammed to customers with no intended function. The customers then configure these devices to implement their unique system design and evaluate the results. If a feature changes or a bug is discovered, the user can simply load a new configuration to the FPGA to create a new product. This process can be repeated until an ideal system has been achieved, giving the designer the flexibility to make changes very late in the design cycle and even after product shipment in the form of firmware upgrades.

#### 2.1 Introduction

FPGA configuration creates digital circuits described in Hardware Description Languages (HDL) and should be distinguished from loading any associated software programs. These digital circuits consist of basic components such as logic gates, flip-flops and memories, and wires. There are three types of configuration technologies with each having unique features. Most commonly used the static random access memory (SRAM) is fast and small, and it offers unlimited reprogrammability. One of the drawbacks though is that the FPGA needs time to reload the entire design into SRAM every time the FPGA powers up. This approach also takes more power. Flash and antifuse technologies are non-volatile (meaning that they can retain data even if power is turned off) so that they provide the benefit of "instant on" without needing to reload the FPGA bit file every time we power up the FPGA or system. They also draw less power than the SRAM approach. Antifuse technology can only be programmed once and can't match the performance of SRAM technology. The only reasons to use an antifuse technology FPGA today is due to its super high reliability and security.

FPGA architectures have been intensely investigated over the past two decades. A significant aspect of FPGA architecture research is the development of Computer Aided Design (CAD) tools for mapping applications to FPGAs. It is well established that the quality of an FPGA-based implementation is largely determined by the effectiveness of accompanying suite of CAD tools. Benefits of an otherwise well design, feature rich FPGA architecture might be impaired if the CAD tools cannot take advantage of the feature the FPGA provides. Thus, CAD algorithm research is essential to the necessary architectural advancement to narrow the performance gaps between FPGAs and other computational devices.

The primary alternative to an FPGA is an ASIC (Application Specific Integrated Circuit) that has speed, power and area advantages over an FPGA. Compared to FPGAs, ASICs have certain disadvantages in the form of higher non-recurring engineering (NRE) cost, longer manufacturing time and increasingly complicated design process. In high volumes, ASIC implementations have resulted in the most cost-effective and lower energy solutions. However, increasing costs and the fact that there is no room for error or change once an ASIC is released have made the FPGA a much more attractive solution in specific applications.

#### 2.1.1 FPGA Evolution through the Years

In the 1970s, logic systems were created by building PCB boards consisting of transistor-transistor logic (TTL) logic chips. However, as functions got larger, the logic size and levels increased and thus compromised the speed of the design. Typically, designers used logic minimization techniques, such as those based on Karnaugh maps to create a sum of products expression by generating the product terms using AND gates and summing them using an OR gate.

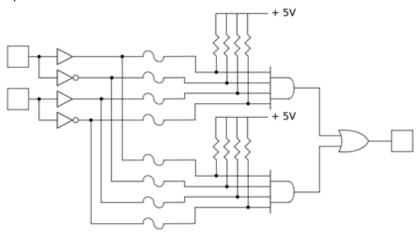

Eight years later a company named Monolithic Memories introduced the concept of creating a structure to achieve implementation of this functionality with a new programmable array logic (PAL). The PAL comprised a sum of products structures to be implemented directly from minimized expression. In Figure 1 the programmable elements (shown as a fuse) connect both the true and complemented inputs to the AND gates. These AND gates, also known as product terms, are ORed together to form a sum-of-products logic array. A matrix with fixed AND and OR gates became the key feature of a class of devices known as programmable logic devices (PLDs).

Figure 1 A simplified programmable logic device. [1]

The initial PLDs could replace ten or so TTL gates and were one time programmable. This led to the reprogrammable PLDs based on EEPROM or EPROM technologies. The PLD structure had a number of advantages. It clearly matched the process of how the sum of products was created by the logic minimization techniques. The function could then be fitted into one PLD device, or, if not enough product terms were available, then it could be fed back into a second PLD stage. Another significant advantage was that the circuit delay is deterministic, either comprising one logic level or two.

As lithography advanced through the years, it enabled a new class of device, the FPGA. FPGAs introduced two important new architecture features: programmable routing to interconnect the increasing number of gates on a device and a programmable gate called a LUT or lookup table with an associated register. A LUT is a small amount of read-only memory. A four-input, one output LUT can generate any four input Boolean function. It is also small enough to achieve efficient utilization of the chip area, but large enough to implement a reasonable range of functions. If a higher number of inputs is required, then LUTs are cascaded together to provide implementation, but at a lower speed. This was judged to provide an acceptable trade-off. The initial devices from Xilinx contained up to a hundred LUT and flip-flop pairs in a basic logic element called CLB or configurable logic block. Rather than using a permanently programmed EPROM or EEPROM memory, Xilinx relied on CMOS memories to hold programming information. The first commercial concept emerged in 1985 with the XC2064 FPGA family from Xilinx which had 64 programmable logic cells. At the same time, Altera was also developing a programmable device later to become the EP1200, which was the first high-density programmable logic device (PLD).

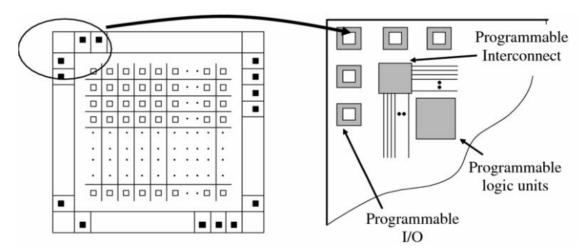

The early FPGA offerings were based on the Manhattan-style architecture (Figure 2) where each individual cell comprised simple logic structures and cells were linked by programmable connections. Thus FPGA could be viewed as comprising the following:

- programmable logic units that can be programmed to realize different digital functions

- programmable interconnect to allow different blocks to be connected together

- programmable I/O pins.

Figure 2 Early Manhattan architecture. [2]

This was ideal for situations where FPGAs were viewed as glue logic as programmability was then the key to provide redundancy and protection against PCB board manufacture errors, it might even provide a mechanism to correct design faults. However, technology evolution, outlined by Moore's law, now provided scalability for FPGA vendors. During the 1980s, this was exploited by FPGA vendors in scaling their technology regarding numbers of interconnectivity and number of I/Os. Nonetheless, it was recognized that this approach had limited scope, as scaling meant that interconnect was becoming a major issue and technology evolution now raised the interesting possibility that dedicated hardware could be included, such as dedicated multipliers and, more recently ARM processors. In addition, the system interconnectivity issue would be alleviated by including dedicated interconnectivity in the form of Serializer/Deserializer and RapidIO.

At an early stage, the FPGA market was populated by a number of vendors, including Xilinx, Altera, Actel, Lattice, Crosspoint, Prizm, Plessey, Toshiba, Motorola, Algotronix and IBM. However, the costs of developing technologies not based on conventional integrated circuit design processes and the need for programming tools saw the demise of many of these vendors and a reduction in the number of FPGA families.

The FPGA took its place as a central component in digital systems, replacing PLDs and TTL for implementing glue logic. In the 1990s new uses began to emerge for FPGAs, which were becoming more capable than just gluing I/O to processors. The emerging Internet became a growth driver for FPGAs with FPGAs being used for prototyping, initial deployment, and full-scale production of Internet switches and routers. By 2000 communications systems were the primary market for FPGAs. Other new markets for FPGAs also emerged for ASIC prototyping and high-performance DSP (digital signal processing) systems. FPGAs also began to be used for implementing soft control processors such as the Xilinx Microblaze and PicoBlaze architectures. As of today, the market is dominated by Xilinx and Altera and more importantly, the FPGA has grown from a simple glue logic component to a complete system on chip (SoC) comprising onboard physical processors, soft processors, dedicated DSP hardware, memory and high speed I/O.

#### 2.1.2 Basic Components

The computing functionality in an FPGA is provided by its programmable logic blocks and these blocks connect to each other through programmable routing network. Modern FPGAs include unique components that cater specific needs to cover a broad spectrum of applications.

#### **Programmable Interconnect:**

FPGAs are built around an array of programmable logic blocks embedded in a sea of programmable interconnect. This array is often referred to as the programmable logic fabric (PL) or just the fabric. At the edges are programmable I/O blocks design to interface the fabric signals to the external world. Interestingly, nearly all the other special FPGA features such as carry chains, block RAM, or DSP blocks can also be implemented in programmable logic. This is in fact the approach the initial FPGAs took and users did implement these functions in LUTs. However, as the FPGA markets developed, it became clear that these special functions would be more cost effective as dedicated functions build from hard gates and later FPGA families such as the Xilinx 4K series and Virtex began to harden these special functions. This hardening improved not only the cost but also improved frequency substantially.

Within any one FPGA family, all devices will share a typical fabric architecture, but each device will contain a different amount of programmable logic. This enables the user to match their logic requirements to the right-sized FPGA device. FPGAs are also available in two or more package sizes which allow the user to match the application – I/O requirements to the device package. FPGA devices are also available in multiple speed grades and multiple temperature grades as well as multiple voltage levels. The highest speed devices are typically 25% faster than the lower speed devices. By designing to the lowest speed, users can save on cost, but the higher performance of faster devices may minimize the system level cost. Modern FPGAs commonly operate at 100-500 MHz. In general, most logic designs which are not targeted at FPGA architectures will run at lower frequency range, and designs targeted at FPGAs will run in the mid-frequency range. The highest frequency designs are typically DSP designs explicitly constructed to take advantage of FPGA DSP and BRAM blocks.

A high-level overview of FPGA architectures can be split into different pieces. Starting at the foundation, the Programmable Interconnect is a set of wires woven through the FPGA logic fabric which can be wired together to connect any two blocks in an FPGA. This enables arbitrary logic networks to be constructed by the user. The architecture of the interconnect wires varies from generation to generation and is hidden from the user tools.

#### **Programmable Logic Blocks:**

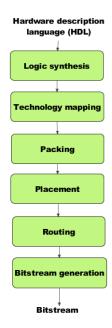

An array of programmable logic blocks are embedded into the Programmable Interconnect and form the main logic resources for implementing sequential as well as combinatorial circuits. These are called CLBs (configurable logic blocks) in Xilinx devices. Today, each logic block consists of one or more programmable logic functions implemented as a 4-6 bit configurable lookup table (LUT), a configurable carry chain, and configurable registers. We use the word configurable to indicate a hard block which can be configured through the FPGA's configuration memory to be used as part of the user's logic. The combination of a LUT, carry chain, and register is called a logic cell or LC. The capacity of FPGAs is commonly measured in logic cells. For instance, Xilinx Virtex UltraScale FPGA supports up to 4 million LCs, while the smallest Spartan device contains as few as 2000 logic cells. Depending on usage, each logic cell can map between 5 and 25 ASIC gates. The lower number is commonly used for ASIC netlist emulation, while the higher number is achievable under expert mapping. For Xilinx UltraScale devices, the CLB supports up to 8 x 6-input LUTs, 16 registers, and 8 carry chain blocks. Each 8-LUT can be configured as 2 x 5-LUTs if the 5-LUTs share common signals. Figure 3 illustrates the UltraScale CLB architecture.

Embedded in the CLB is a high-performance look-ahead carry chain which enables the FPGA to implement very high-performance adders. Current FPGAs have carry chains which can implement a 64-bit adder at 500MHz. Associated with each LUT is an embedded register. The rich register resources of the FPGA programmable logic enable highly pipelined designs, which are a key to maintaining higher speeds. Each register can be configured to support a clock enable and reset with configurable polarity.

An important additional feature of the Xilinx CLB's 6-LUT is that it can configure to implement a small 64-bit deep by 1-bit wide memory called a distributed RAM. An alternate configuration allows the 6-LUT to implement a configurable depth shift register with a delay of 1-32 clocks.

Access to memory is critical in modern logic designs. Programmable logic designs commonly use a combination of memories embedded in the FPGA logic fabric and external DDR memories. Within the logic fabric, memory can be implemented as discrete registers, shift registers, distributed RAM, or block Ram. Xilinx UltraScale devices support two sizes of block RAM, 36-kbit RAMs, and 288-kbit RAMs. In most cases, the Xilinx tools will select the best memory type to map each memory in the user design. In some cases, netlists optimized for FPGAs will hand instantiate memory types to achieve higher density and performance.

Special forms of memory called dual-port memories and FIFOs are supported as special modes of the block RAMs or can be implemented using distributed RAM. System memory access to external DDR memory is via a bus interface which is commonly an AXI (advanced Xilinx interface) protocol to the FPGA. UltraScale FPGAs support 72-bit wide DDR4 at up to 3200 MB/s.

In general, registers or flip-flops are used for status and control registers, pipelining, and shallow (1-2 deep) FIFOs. Shift registers are commonly used for signal delay elements and pipeline balancing in DSP designs. Distributed RAMs are used for shallow memories up to 64 bits wide and can be as wide as necessary. Block RAMs are used for buffers and deeper memories. They can also be aggregated together to support arbitrary widths and depths. For instance, a 64-bit wide by 32 K-bit deep memory would require 64 block RAMs. Generally, FPGAs contain around 1 36 K block RAMs for every 500-1000 logic cells.

Figure 3 UltraScale CLB architecture. [3]

#### Digital Signal Processing:

Modern FPGAs contain discrete multipliers to enable efficient DSP processing. Commonly DSP applications build pipelines or flow graphs of DSP operations and data streams through this flow graph. A typical DSP filter called FIR (finite impulse response) filter, it consists of sample delay blocks, multipliers, adders, and memories for coefficients. Interestingly it can be implemented almost directly as an FPGA circuit. For filtering and many other DSP applications, multiplies and adders are used to implement the flow graph. Xilinx FPGAs contain a DSP block

known as a DSP48 which supports an 18-bitx 25-bit multiplier, a 48-bit accumulator, and a 25-bit pre-adder. In addition up to four levels of pipelining can be supported for operation up to 500 MHz. The DSP48 supports integer math directly; however, 32-bit and 64-bit floating point operations are supported as library elements. A 32-bit floating point multiplier will require two DSP48s and several hundred LCs.

Xilinx tools will generally map multipliers and associated adders in RTL or HDL languages to DSP48 blocks. For highest performance however, designs optimized for DSP in FPGAs may use DSP48 aware libraries for optimal performance, power, and density.

#### **Clock Management:**

Logic netlists almost universally require one or more system clocks to implement synchronous netlists for I/O and for internal operation. The synchronous operation uses a clock edge to register the results of upstream logic and hold it steady for use by downstream logic until the next clock edge. The use of synchronous operation allows for pipelined flow graphs which process multiple samples in parallel. External digital communications interfaces use I/O clocks to transfer data to and from the FPGA. Commonly, interface logic will run the I/O clock rate (or a multiple of the I/O clock rate).

#### I/O blocks:

One of the critical capabilities of FPGA is that they interface directly to external input and output (I/O) signals of all types and formats. To support these diverse requirements, modern FPGAs contain a special block called the I/O block or IOB. This block contains powerful buffers to drive external signals out of the FPGA and input receivers, along with registers for I/O signals and output enables (OE). IOBs typically support 1.2- 3.3 V CMOS as well as LVDS and multiple industry I/O memory standards such as SSTL3. I/Os are abstracted from the user RTL and HDL design and are typically configured using a text file to specify each I/O's signaling standard.

UltraScale devices also include multiplexing and demultiplexing features in the I/O block. This feature supports dual data rate (DDR) operation and operation for 4:1 or 8:1 multiplexing and demultiplexing. This allows the device to operate at a lower clock rate than the I/O clock. For example, Gigabit Ethernet (SGMII) operates at 1.25 GHz over a single LVDS link, which is too fast for the FPGA fabric to support directly. The serial signal is expanded to 8/10 bits in the IOB interface to the fabric allowing the fabric to operate at 125 MHz.

I/Os are commonly a limited resource and FPGAs are available in multiple package sizes to allow the user to use smaller lower-cost FPGAs with lower signal count applications and larger package sizes for higher signal count applications. This helps to minimize system cost and board space. A primary application of FPGA I/Os is for interfacing to memory systems. UltraScale devices support high-bandwidth memory systems such as DDR4.

#### High-Speed Serial I/Os (HSSIO):

CMOS and LVDS signaling are limited in performance and can be costly in terms of power and signal count. For this reason, high-speed serial I/Os have been developed to enable low-cost, high-bandwidth interfaces. This evolution can be seen in the evolving PCI standard which has moved from low-speed 32-bit CMOS interfaces at 33 MHz to PCIe Gen3 with 1-8 lanes at Gb/s lane. An eight-lane PCIe Gen3 interface can transfer 64 Gb/s of data in each direction. Xilinx UltraScale devices support up to 128 MGT (Multi-Gigabit Transceivers) at up to 32.75 Gb/s.

Within the FPGA, the HSSIO are interfaced directly to a custom logic block which multiplexes and demultiplexes the signals to wide interfaces at lower clock rates.

## 2.1.3 Uses and Application Fields

FPGAs are used extensively for computing problems that benefit from parallel computer architectures due to their parallel nature and optimality in terms of the number of gates used for a certain process. An FPGA can even be proven faster than a computer if the tasks are separated into discrete pieces. Another aspect of FPGAs that is now on the rise is hardware acceleration, where one can use the FPGA to accelerate certain parts of an algorithm and share part of the computation between the FPGA and a generic processor. Furthermore, reusability of the FPGA is a crucial advantage. Prototypes of a design can be implemented on FPGAs, which then can be verified to closely replicate how an ASIC would behave. In case of design faults, new versions can be created by changing the HDL code, generating a new bitstream, and configuring the FPGA in order to test it again since modern FPGAs are reconfigurable both partially and on the fly. A new design can be uploaded even remotely, instantly due to FPGAs field reprogram ability. This is very useful in cases that the designer cannot physically access the FPGA for example in a satellite that orbits earth or if a product has been released and needs an update.

FPGAs have justly gained their own position as suitable platforms to deal with increasingly complex control tasks and are also getting at very fast pace, into the world of High-Performance Computing (HPC). This technological trend has also extended the applicability of FPGAs in their original application domains. For instance, emulation techniques are evolving into mixed solutions, where the behavior or parts of a system can be evaluated by combining simulation models with hardware emulation, in what is nowadays referred to as hardware-in-the-loop (HIL). Tools exist, including some of general use in engineering, such as MATLAB, which allow this combined simulation/emulation approach to be used to accelerate system validation.

FPGAs are also increasingly penetrating the area of embedded control systems because in many cases, they are the most suitable solution to deal with the growing complexity problems to be addressed in that area. Some important fields of application (not only regarding technical challenges but also in terms of digital systems market share) are in automated manufacturing, robotics, control of power converters, motion and machinery control, and embedded units in automotive. It is worth noting that a modern car has some 70-100 embedded control units onboard. As the complexity of the systems to be controlled grows, microcontroller and DSPs are becoming less and less suitable, and FPGAs are taking the floor.

A clear proof of the excellent capabilities of current FPGAs is their recent penetration in the area of HPC, where a few years ago, no one would have thought they could compete with software approaches implemented in large processor clusters. However, computing-intensive areas such as big data applications, astronomical computations, weather forecast, financial risk management, complex 3D imaging (e.g., in architectures, movies, virtual reality, or video games), traffic prediction, earthquake detection, and automated manufacturing may currently benefit from the acceleration and energy efficient characteristics of FPGAs.

Traditionally, FPGAs have been reserved for specific industries and markets where the volume of production is small. For these low-volume applications, the premium that companies pay in hardware costs per unit for a programmable chip is more affordable than the development resources spent on creating an ASIC for the low-volume application. Today, new cost and performance dynamics have broadened the range of viable applications such as:

- ASIC prototyping.

- Wired communications: for system development, while the standards themselves are evolving.

- Wireless communications: DSP in FPGAs is a major attraction for algorithmic computations.

Video systems and machine vision: Implement software algorithms at higher speed and lower power.

- Industrial systems: Communication link between sensor nodes and robotic systems.

- Medical systems: I/O interfaces including A-to-D and D-to-A conversion.

- Automotive systems: video processing for driver assistance.

- Military and aerospace: Radio waveform processing and processing of huge amounts of sensor data.

- Data center: Interfaces to SSD, machine learning related algorithms.

#### 2.2 FPGA Development Flow.

Tools and methodologies for FPGA-based design have been continuously improving over the years for them to accommodate the new and extended functionality requirements imposed by increasingly demanding applications. Today's designs would take unacceptable extremely long times to be completed if tools coming from more than 20 years ago were used. The first important incremental step in accelerating design processes was the replacement of schematic-based design specifications by HDL descriptions. On the one hand, this allows complex circuits described at different levels of abstraction to be more efficiently simulated, and on the other hand, designs to be quite efficiently translated by means of synthesis, mapping, placement, and routing tools from HDL into netlists, as a step previous to its translation into the bitstream with which the FPGA is configured.

Designers quite rapidly adopted conventional synthesis tools due to the productivity jump they enabled. At that point, it soon became apparent that FPGAs were very well suited to rapid prototyping and emulation flows because very little HDL code rework (or even none at all) was required in order to migrate designs initially implemented in FPGAs to other technologies. Either for prototyping or final deployment, FPGAs rapidly increased their manufacturing share. As a consequence, and thanks to the improvement of manufacturing technologies, their complexity was continuously increased to cope with the ever-growing demand for more and more complex integrated systems. This in turn, contributed to higher market penetration, which pushed for additional complexity and expanded functionality.

The fast adoption of conventional synthesis tools as part of the natural design process for all types of digital hardware devices was not as fast in the case of High-Level-Synthesis (HLS) tools. The difference between both types of tools resides in clock cycle explicitness. A conventional synthesizable HDL file mostly consists of descriptions where the transfers between memory elements can be directly and explicitly inferred from the code, clock cycle by clock cycle. In contrast, HLS tools start from descriptions that do not explicitly specify clock activity but work at algorithmic level instead. The contribution or refinement HLS tools provide their ability to allocate logic resources or operators and assign functions to such operators within the required time slots so that the algorithm may be mapped to a circuit with efficient resource sharing. Additionally, logic functions can be extended into optimized pipelined structures (so that the translation of such slots into clock cycles makes timing explicit), and clock speed can be optimized by adequately balancing critical paths within the pipelined structures. Regarding memories, different accessing schemes enable variable bandwidth adjustment so that it may fit appropriately to the functions being carried out by the logic reading/writing data from/to such memories. Finally, HLS tools also support two I/O types: memory mapped and stream based.

Traditional or HLS tools alone cannot support the design of many of today's complex FPGA embedded systems. They need to be combined with platform-based tools that, in essence, automate different processes within the FPGA design flow. These tools combine standard

components from integrated IP libraries with custom-made block designed using either conventional or HLS flows. Most current embedded systems are not fully customized designs, but rely on the combination of some standardized functions and interfaces with custom-made IP blocks. Therefore, module reuse and automated tools are mandatory in order to speed up the design process. Complex systems may be built with relatively little designer intervention if the design is based on library modules connected with standardized on-chip interfaces. These tools provide, among many other features, module customization, automatic connection, automated memory map generation, as well as easy access to software code programmers using hardware abstraction layers for easy hardware/software interfacing. This design methodology allows highly complex designs to be readily obtained, for instance, a dual-core processor system with complex DMA schemes providing efficient access to a gigabit Ethernet media access control layer, plus some other I/O interfaces ( such as SPI, I²C, USARTS, or GPIO), can be built in only a few hours.

Other tools are currently available whose design languages allow explicit parallelism to be described, aimed at achieving the maximum algorithm acceleration in HPC applications. They are based on OpenCL, which allows multithread parallelism to be mapped to heterogeneous computing platforms, such as FPGAs. In the last years, the leading FPGA vendors are continuously releasing new specialized tools to ease the translation from OpenCL code into FPGA designs. These tools provide ways for designs running in a host usually a computer, to be accelerated by attaching one or more FPGA boards to it, often using PCIe connections.

Increasingly, complex tools and design flows must necessarily be complemented with proper validation and debugging methods. Verification can (and should) be done at early design stages, prior to circuit configuration, by means of simulation techniques. These techniques may be performed at functional level, to validate logic functionality, or after placement and routing, where accurate timing data are available to be annotated into the simulation. Very interestingly, it is also possible to use integrated logic analyzers (embedded into the FPGA) for debugging purposes. These elements allow for combined hardware/software evaluation, which is very useful, especially for field-programmable SoC designs.

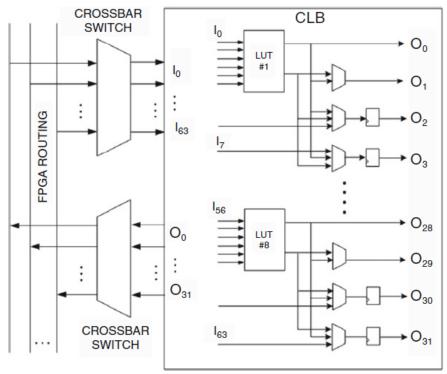

One of the major research aspects of FPGAs is the development of software flow required to map hardware applications on an FPGA. The effectiveness and quality of an FPGA are mainly dependent on the software flow provided with an FPGA. The software flow takes an application design description in a Hardware Description Language (HDL) and converts it to a stream of bits that is eventually programmed on the FPGA. Figure 4 shows a complete software flow for programming an application circuit on an FPGA. A brief description of various modules of software flow is described below.

Figure 4 FPGA software configuration flow.

#### Logic synthesis:

Logic synthesis transforms an HDL description (VHDL or Verilog) into a set of Boolean gates and flip-flops. The synthesis tools transforms the register-transfer-level (RTL) description of a design into a hierarchical Boolean network. Various technology-independent techniques are applied to optimize the Boolean network. The typical cost function of technology-independent optimizations is the total literal count of the factored representation of the logic function. The literal count correlates very well with the circuit area.

#### **Technology mapping:**

After logic synthesis, technology-dependent optimizations are performed. These optimizations transform the technology-independent Boolean network into a network of gates in the given technology library. The technology mapping for FPGAs transforms the given Boolean network to the available set of blocks on an FPGA. For a traditional FPGA architecture, the Boolean network is transformed into Look-Up tables and flip-flops. Given a library of cells, the technology mapping problem can be expressed as finding a network of cells that implement the Boolean network. In the FPGA technology mapping problem, the library of cells is composed of k-input LUTs and flip-flops. Therefore, FPGA technology involves transforming the Boolean network into k-bounded cells. Each cell can then be implemented as an independent k-LUT. Technology mapping algorithms optimize a given Boolean network for a set of different objective functions including depth, area and power. The FlowMap algorithm is the most widely used academic tool for FPGA technology mapping. FlowMap is a breakthrough in FPGA technology mapping because it is able to find a depth-optional solution in polynomial time. The final output of FPGA technology mapping is a network of I/Os, LUTs, and flip-flops.

## Clustering/Packing:

The logic elements in a mesh-based FPGA are typically arranged in two levels of hierarchy. The first level consists of logic cells which are k-input LUT and flip-flop pairs. The second level hierarchy groups k logic cells together to form logic cell clusters. These clusters can then be directly mapped on the CLBs of an FPGA. The main optimization goal is to cluster the LUTs, flip-flops and logic cells in such a way that inter-cluster communication is minimized. Less inter-cluster communication ensures less routing resource utilization in an FPGA. There are also

different approaches to clustering algorithms that achieve specific features based on the needs of the application. These algorithms can be broadly categorized into three general approaches, namely top-down, depth-optimal and bottom-up. Top-down approaches partition the logic cells into clusters by successively subdividing the network or by iteratively moving logic cells between parts. Depth-optimal solutions attempt to minimize delay at the expense of logic duplication. Bottom-up approaches are generally preferred for FPGA CAD tools due to their fast run times and reasonable timing delays. They only consider local connectivity information and can easily satisfy clusters pin constraints. Top-down approaches offer the best solutions. However, their computational complexity can be prohibitive. The final output of packing is a network of I/Os and CLBs.

#### Placement:

The placement algorithm determines the position of CLB and I/O instances in a packed netlist on the respective CLB and I/O blocks on the FPGA architecture. The main goal of placement algorithm is to place connected blocks near each other so that minimum routing resources are required to route their connections. The placement algorithm can also serve to fulfill other architectural or optimization requirements, such as balancing the wire density across FPGA.

Three major types of commonly used placement algorithms are (I) min-cut (partitioning) based placement algorithm which is an approach suitable for hierarchical FPGA architectures. The partitioner is recursively applied to distribute netlist instances between clusters. The aim is to reduce external communication and merge highly connected instances in the same cluster. (II) Analytical placement algorithms commonly utilize a quadratic wire length objective function. Although, a quadratic objective is only an indirect measure of the wire length; its main advantage is that it can be minimized very efficiently and is this suitable for handling massive problems. A quadratic function does not give the best possible wire length, and it is often followed by some local iterative improvement techniques. (III) The simulated annealing placement algorithm uses the annealing concept for molten metal which is cooled down gradually to produce high-quality metal objects. The simulated annealing algorithm is very effective at finding an acceptably good solution in a limited amount of time. The algorithm is also good at approximating an acceptable placement solution for a netlist to be placed on an FPGA. A wire length cost function is used to measure the quality of the placement. Netlist instances are initially placed randomly on the FPGA. Different instance moves are made to gradually improve the quality of the placement.

#### Routing:

Once the instances of a netlist are placed on FPGA, connections between different instances are routed using the available routing resources. The FPGA routing problem consists of routing signals (or nets) in such a way that no more than one signals use the same routing resource. PathFinder routing algorithm is commonly used for FPGAs. In order to perform routing on FPGA architecture, the routing architecture is initially modeled as a directed graph where different nodes are connected through edges. Each routing wire of the architecture is represented by a node, and the connection between two wires is represented by an edge. When a netlist is routed on the FPGA routing graph, each net (i.e., connection of a driver instance with its receiver instances) is routed using congestion driven Dijkstra's "Shortest Path" algorithm. Once all nets in a netlist are routed, one routing iteration is said to be completed. At the end of an iteration, there can be conflicts between different nets sharing the same nodes. The congestion parameters of the nodes are updated, and routing iterations are repeated until routing converges to a feasible solution (i.e., all conflicts are resolved) or routing fails (i.e., maximum iteration count has reached, and few routing conflicts remain unresolved).

#### Timing analysis:

Timing analysis is not a part of the actual software flow since it does not alter the design in any way, but instead, it provides important reports that are crucial to the success of the final result. Timing analysis is used for two basic purposes:

- To determine the speed of circuits which have been completely placed and routed.

- To estimate the slack of each source-sink connection during routing (placement and other parts of the CAD flow) in order to decide which connections must be made via fast paths to avoid slowing down the circuit.

First, the circuit under consideration is presented as a directed graph. Nodes in the graph represent input and output pins of circuit elements such as LUTs, registers and I/O pads. Connections between these nodes are modeled with edges in the graph. Edges are added between inputs of combinational logic blocks (LUTs) and their outputs. These edges are annotated with a delay corresponding to the physical delay between the nodes. Register input pins are not joined to register output pins. To determine the delay of the circuit, a breadth-first traversal is performed on the graph starting at sources (input pads, and register outputs). Then the arrival time which is the time elapsed for a signal to arrive at a certain point is computed with the following equation:

$$T_{arrival}(i) = max_{j \in fanin(i)} \{T_{arrival}(j) + delay(j, i)\}$$

where node i is the node currently being computed, and delay(j,i) is the delay value of the edge joining node j to node i. The delay of the circuit is then the maximum arrival time,  $D_{max}$ , of all nodes in the circuit.

To guide a placement or routing algorithm, it is useful to know how much delay may be added to a connection before the path that the connection is on becomes critical. The amount of delay that may be added to a connection before it becomes critical is called the slack of that connection. To compute the slack of a connection, one must compute the required arrival time,  $T_{required}$ , at every node in the circuit. We first set the  $T_{required}$  at all sinks (output pads and register inputs) to be  $D_{max}$ . Required arrival time is then propagated backwards starting from the sinks with the following equation:

$$T_{required}(i) = min_{j \in fanout(i)} \{T_{required}(j) - delay(j, i)\}$$

Finally, the slack of a connection (i,j) driving node, j is defined as:

$$Slack(i,j) = T_{required}(j) - T_{arrival}(i) - delay(i,j)$$

#### **Bitstream Generation:**

Once a netlist is placed and routed on an FPGA, bitstream information is generated for the netlist. This bitstream is programmed on the FPGA using a bitstream loader. The bitstream of a netlist contains information to program the SRAM bits of Look-Up Tables. The routing information of a netlist is used to correctly program the SRAM bits of connection boxes and switch boxes.

#### 2.3 Partial Reconfiguration.

The configuration possibilities offered by FPGAs created a new paradigm in digital circuit design since the same device (i.e., the same hardware) can be adapted to provide different functions by just reconfiguring it. In other words, a device may implement different functions in the course of its operation, allowing it to be adapted to different operating conditions in response to modifications in the required functionality, changes in the environment, or even faults that might take place, therefore allowing its usability to be extended.

When hardware reconfiguration capabilities are required for a given application, the use of FPGAs offers many advantages and opportunities. Although reconfigurable systems are not

limited to just FPGA-based ones, these are the most significant at a commercial level. Other possibilities exist, based on custom devices with specific reconfiguration features, mainly oriented toward reconfigurable computing systems. However, these devices are intended to overcome some limitations of FPGAs in very specific areas, for instance ultrafast reconfiguration time (i.e., reconfiguring a complete device in just one clock cycle). Coarse-grained reconfigurable architectures are an example of this, where different functions are implemented in the same silicon die so that the resulting system may be adapted to changing conditions. These solutions have limited flexibility because the functions are decided at design time and can be neither be changed nor modified once the device is manufactured. On the other hand, the configurability of most FPGAs of truly reconfigurable devices in general allows the functions to be performed by the system to be adapted at any moment during its lifetime, even during infield operation.

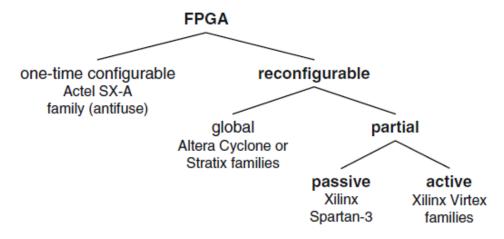

Based on the ability of reconfiguration a new concept emerged. Partial reconfiguration takes it one step further and allows the dynamic modification of part of an operating FPGA design without impacting the rest of the design. Summing all the architectures so far we can classify them with respect to their configuration capabilities, as illustrated in Figure 5. At the highest level, FPGAs can be separated into one-time configurable devices that can only be used as an ASIC substitute and configurable FPGAs. Configurable FPGAs can in turn be distinguished in globally and partially reconfigurable devices. When globally reconfiguring an FPGA, the complete device configuration is exchanged. As a consequence, all the internal states get lost and the FPGA will have to restart its operation. This is appropriate for an in-field update of the FPGA but is unlikely for self-adapting reconfigurable systems. For the purposes of this thesis, we will focus mostly on partial reconfiguration.

From the perspective of the design functionality, partial reconfiguration can be split into parts:

- Static Partial reconfiguration (passive), the FPGA is stopped during the reconfiguration process. While the partial portion of data is sent into the device, the rest of the FPGA is in the shutdown mode. The device is brought up after the partial configuration is completed.

- Dynamic partial reconfiguration (active), the FPGA is active during the reconfiguration process. While the part of the device is being reconfigured, the rest of the FPGA is still running. In other words, dynamic partial reconfiguration permits configuration of the FPGA without stopping of the device.

Figure 5 Classification of FPGAs by their configuration capabilities. [3]

## 2.3.1 Partial Reconfiguration Fundamentals

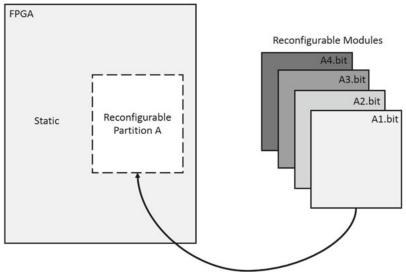

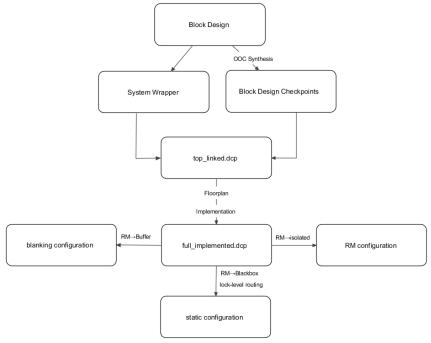

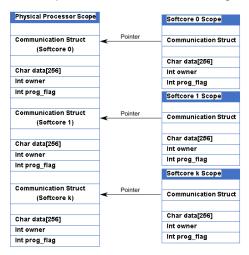

All partial reconfiguration designs consist of three basic parts. The Static is portion of the design that does not change and is expected to continue to function at all times. The Reconfigurable Partition is the instance or level of hierarchy within which multiple Reconfigurable Modules are defined and implemented. Each Reconfigurable Module represents one of the time-multiplexed functions that will be switched in and out of the FPGA (Figure 6).

Figure 6 Basic partial reconfiguration concept and terminology. [5]

Partial reconfiguration designs can contain one or more reconfigurable partitions, each of which must occupy a mutually exclusive physical area of the FPGA. The physical area for a given reconfigurable partition must contain the aggregated resources required to individually implement each of the reconfigurable modules associated with it. The resource types and granularity of the physical area within the FPGA that can be reconfigured at any given time vary by device family.

Both Static and the interface points between the Static and the reconfigurable partition need to be identical for all the reconfigurable modules in the design. Vivado achieves this by preserving the static implementation and reusing it to implement subsequent reconfigurable modules. An additional innovation in Vivado is the creation of virtual I/O for each of the interface port called a Partition Pin. Partition Pins can be locked to specific anchor points within the routing tiles and maintained across reconfigurable modules. This consumes no LUTs or flip-flops, thus reducing resource overhead and timing delays at the interface.

Vivado generates a partial bitstream file for each reconfigurable module in each reconfigurable partition as well as a full bitstream which contains the data for both the static and the reconfigurable module(s) being implemented. The full bitstream is used for initial configuration of the FPGA, while the partial bitstreams are used for switching in and out of the various reconfigurable modules. Loading of partial bitstreams into the FPGA is generally performed via the FPGA's standard external configuration ports or via internal configuration ports which can be incorporated into the static portion of the design.

Partial reconfiguration takes advantage of the FPGA's addressable configuration infrastructure which allows specific areas of the FPGA to be configured. The smallest addressable segment of the FPGA is known as a configuration frame. Each frame typically corresponds to a single column of resource type, for example, DSP, block RAM, CLB, or routing interconnect; the actual number of resources in each frame depends on the resource type and varies by device family.

#### 2.3.2 Configuration Mechanisms

Storing and managing partial bitstreams is key to the success of partial reconfiguration in a design. Storage of partial bitstreams is typically outside the FPGA, either on a nonvolatile flash memory on the board or on another remote medium, and accessible to the FPGA via PCIe, Ethernet, SD card, or other data transfer protocol. Managing these partial bitstreams can be done using an external processor or an internal state machine or processor within the static region of the FPGA. The processor or state machine determines which reconfigurable module should be loaded, where the partial bitstream for that reconfigurable module resides as well as when and how it will be downloaded into the FPGA's configuration memory. IP blocks provided by manufacturers such as the partial reconfiguration controller IP from Xilinx can also be used to help manage the partial bitstream configuration.

Depending on the location of the partial bitstreams and the management engine used, various configuration ports can be used to configure the FPGA. The following are the available configuration ports:

- ICAP (internal configuration access port): The primary choice where configuration management is being done internally to the FPGA. This requires a controller as well as logic to drive the ICAP interface.

- MCAP (media configuration access port): Provides access to configuration memory from one specific PCIe block only in UltraScale devices.

- PCAP (processor configuration access port): The primary configuration mechanism for Zynq-7000 SoC designs.

- JTAG: Test and debug port. Mainly driven by the Vivado Hardware Manager.

- Slave SelectMAP or slave serial: A good choice to perform full and partial reconfiguration, especially when using an external processor.

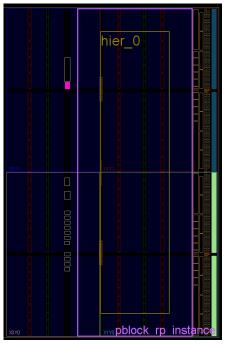

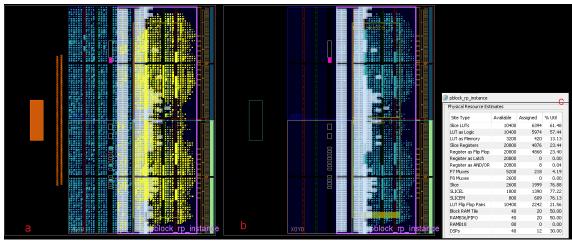

#### 2.3.3 Floorplaning for Reconfigurable Designs

While static-only FPGA-based systems may be implemented without additional area constraints in a completely automatic fashion with the help of a placer tool, floorplanning is essential when designing runtime reconfigurable systems. In this case, all partial modules have to be constrained into bounding boxes and during the implementation of the static part of the system, the assigned reconfigurable area must be prohibited for implementing any static logic or routing.

Floorplanning typically starts with a preliminary synthesis run for budgeting the resource requirements of the static system and of all reconfigurable modules individually. Based on this initial resource budgeting, the target FPGA can be selected. On this target, one or more reconfigurable areas have to be defined that will be tiled into a grid of resource slots. In this step, the system is split into a static part and a dynamically reconfigurable part containing the FPGA resources that are shared by multiple modules over time. These slots will accommodate the partial modules and the grid must provide sufficient resources to fulfill all logic and memory requirements.

#### 2.3.4 Reconfigurable Families

From the commercial point of view, major manufacturers embraced this ability and offered reconfiguration support on their devices. Altera's Excalibur was the company's first devices that allowed the whole FPGA fabric to be dynamically configured from the on-chip hard processor at any moment, by retrieving the corresponding bitstream from an external nonvolatile memory. Later, some Altera devices started to provide limited partial reconfiguration capabilities by allowing specific elements, such as serializers/deserializers or PLLs, to be reconfigured. More recently, Altera V devices (Stratix V, Arria V, and Cyclone V families) extended the support for partial reconfiguration.

A different approach is used by Atmel's FPGAs, which implement partial run-time-reconfiguration through cache logic designs, where part of the FPGA fabric can be reconfigured without loss of register data, while the remainder of the fabric continues to operate without disruption. The main drawback of these in addition, small FPGAs in this context is that the reconfiguration access method is bit based, which requires very low-level reconfiguration control, although it has the advantage of providing very high flexibility.

Most Xilinx SRAM-based FPGAs can be partially reconfigured. This is the reason why they are used in the majority of applications where this feature is required. Their configuration bitstream format allows a designer to modify one or more configuration packets and perform partial reconfiguration by accessing specific portions of the FPGA configuration memory. Each Xilinx device family has different reconfiguration features:

- The low-cost Spartan 3 series supports the reconfiguration of entire columns, including top and bottom I/O blocks. The first Spartan 3 family does not include an ICAP, and thus it is not well suited to designing self-reconfigurable systems.

- All Xilinx high-performance FPGA families provide glitch-less reconfiguration and include an ICAP. Virtex-II and Virtex-II Pro families implement column-based reconfiguration, whereas in the more recent families (Virtex-4, Virtex-5, and all Series 7 families: Artix, Kintex, Virtex, Zynq, and UltraScale), reconfiguration frames do not span entire columns, but several rows are associated with clock domains that are horizontally laid across the FPGA layout. As for clock domains, frames for different families are of different sizes (16 rows for Spartan-6, 20 for Virtex-5, 40 for Virtex-6, 50 for Zynq and former series 7 devices, and up to 60 for UltraScale).

- Some devices have double ICAP support, which may be useful for increased fault tolerance. Zynq devices also have a PCAP, controlled from the processing system, in addition to the conventional ICAP.

Device improvements in this area are slow, mostly pushed by the research community's efforts regarding architectures, tools, and applications.

#### 2.3.5 Benefits of Partial Reconfiguration

In the early days of field programmable gate arrays, the available logic capacity was very limited and using runtime reconfiguration had been suggested to raise resource utilization or to squeeze larger circuits into the available logic. For example, the dynamic instruction set computer (DISC) is capable of changing its instruction set at runtime according to a running program. Consequently, only the currently used instructions are loaded on the FPGA which takes fewer resources than having a system providing all instructions at the same time. However, for decades implementing such systems required deep knowledge about the used FPGA architecture and had to follow an error prune difficult design flow. Furthermore, long configuration time was another crucial issue that detained the use of runtime reconfiguration in industrial applications.

With the progress in silicon process technology, logic capacity raised steadily while getting cheaper (and often more power efficient per logic cell) at the same time. The capacity for the FPGAs of the Virtex family from Xilinx increased from 93k LUTs [6] on Virtex II XC2V8000 device to 1.2 million LUTs [7] on Virtex 7 XC7V2000T device. Respectively the Stratix family from Altera increased from 79k LUTs [8] on Stratix EP1S80 device to 0.7 million LUTs [9] on Stratix V 5SGXA device. The explosion in capacity removed the pressure on the FPGA vendors to add better support for runtime reconfiguration in their tools and devices. However, by heading beyond 1M LUT devices (million look-up table FPGAs), things are changing dramatically at the moment.

For present high capacity FPGAs, the configuration time required to write tens of megabytes of initial configuration data is too long for many applications and partial reconfiguration can be used to speed up the system start.

A further consequence of having large high-density FPGAs is their higher risk of failure due to single event upsets (SEU). However, SEUs can be detected and compensated with the help of partial runtime reconfiguration (e.g., using configuration scrubbing). Another factor arising for current high capacity FPGAs is a strong relative increase in the static power consumption. The static power consumption is related directly to the device capacity. With the help of partial runtime reconfiguration, a system might be implemented on a smaller and consequently less power hungry device. This will further result in a cheaper system.

The factors fast system start, SEU recovery, and static power consumption force FPGA vendors to enhance the support for runtime reconfiguration. As a consequence, partial reconfiguration will be available in the majority of future FPGA devices and it will be better supported by the corresponding tools.

Besides the mentioned functional aspects, the design productivity of complex multi-million system gates designs can be substantially improved by closely integrating partial design methodologies into the standard FPGA design flow. While present tools support to render the logic synthesis process to a compute farm for fast parallel processing, the place and route phase is mostly implemented as a global optimization process. As a consequence, place and route can take many hours or even days to finish, hence making design respins very costly. However, it is possible for the physical implementation of a design to be precisely constrained for individual modules. In other words we can specify all the resources (including wires of the fabric) that are allowed for the place and route step of each module. This would permit to carry out the place and route process for multiple modules in parallel.

Additionally to application benefits there are some generic advantages of partial reconfiguration to expand such as area and power reduction and performance improvement. Due the increased leakage current in deep sub-micrometer CMOS process technology, static power consumption will dominate the total power consumption. By enhancing device utilization with the help of partial runtime reconfiguration, power and monetary cost could be saved. This is essential when following the trend towards more and more mobile devices. Furthermore, low power consumption results in also lower cooling effort.

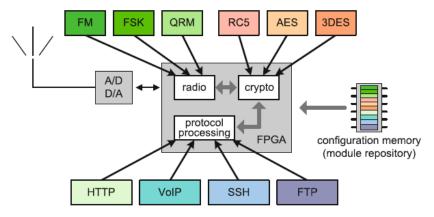

An example of a self-adaptive system featuring a mobile internet device is illustrated in Figure 7. The system provides a software-defined radio part (SDR), different decryption modules, and protocol processing accelerators for various protocols.

Figure 7 Area saving by reconfiguring only the currently required accelerator module to the FPGA. Configurations are fetched from the module repository at runtime. [5]

Assuming that the radio part will be adjusted according to the available bandwidth, and that the crypto and protocol processing accelerators are changed on-demand. We can then save substantial FPGA resources by not providing all variants in parallel, but by only loading the currently required modules to the device. This requires that the accelerator modules are either needed exclusively or that the system can time-multiplex the reconfigurable resources by sufficient fast reconfiguration. However, for low power operation, it should be mentioned that the configuration itself requires some power. This includes the power to fetch a configuration from

the configuration memory and the power required by the FPGA itself for the configuration. Furthermore, it should be noted that the reconfigurable part will consume static power without providing useful work during the whole configuration process. If we assume that the system changes its operation modes on human interaction, the update rate will be sufficiently low such that it easily amortizes the configuration power.

There are more potential benefits than only power and cost savings. If we can implement a system with a smaller FPGA, we might be able to use a smaller package which then permits to build the mobile device smaller. Or in the case of more complex systems that demand multiple FPGAs, runtime configuration might be used to achieve a higher level of integration with the goal to save complete FPGAs. This might further simplify the PCB design and also help to save further power. The latter is possible because due to higher integration, we will typically have more on-chip and less off-chip communication thus saving power.

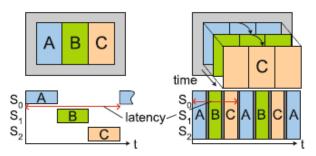

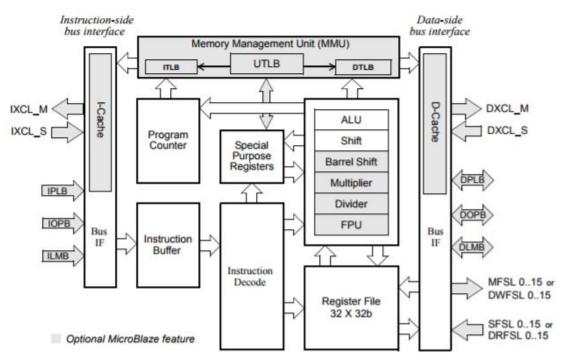

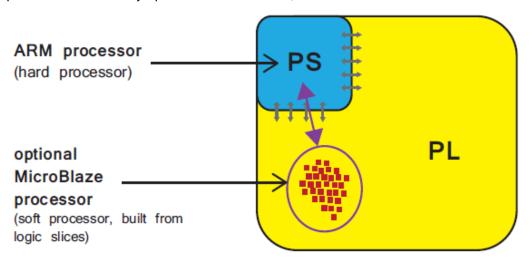

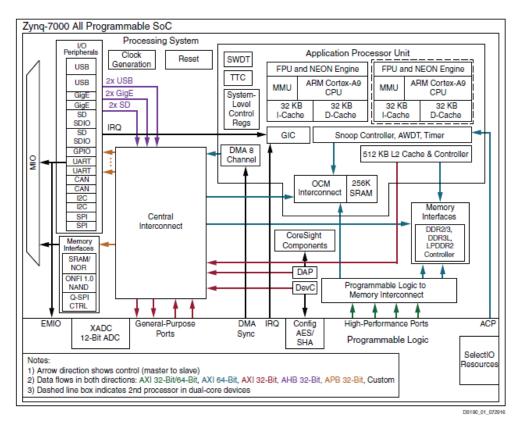

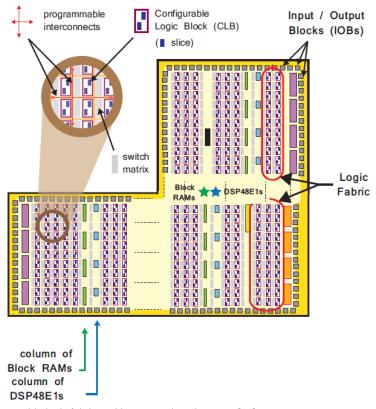

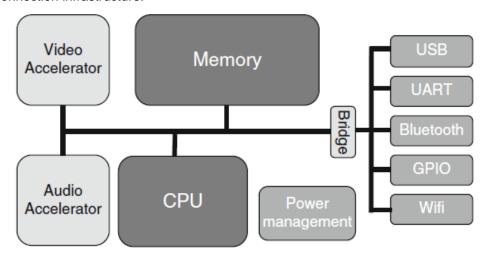

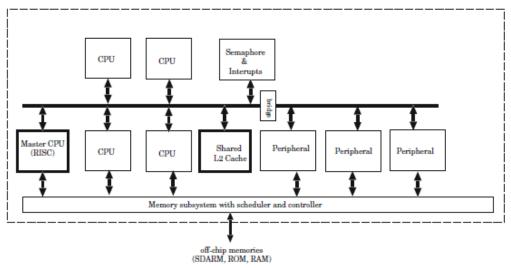

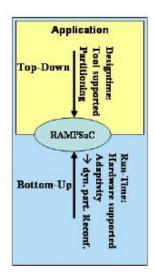

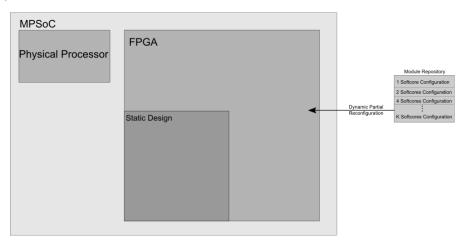

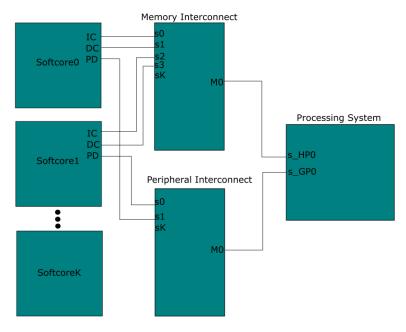

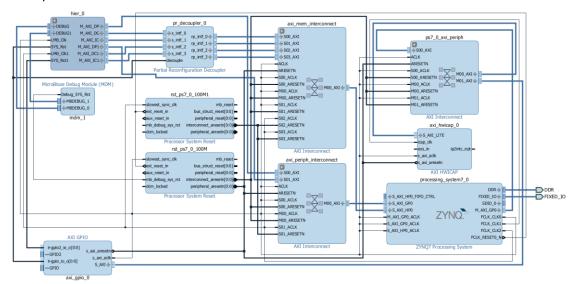

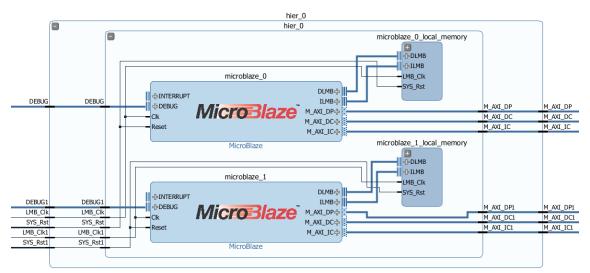

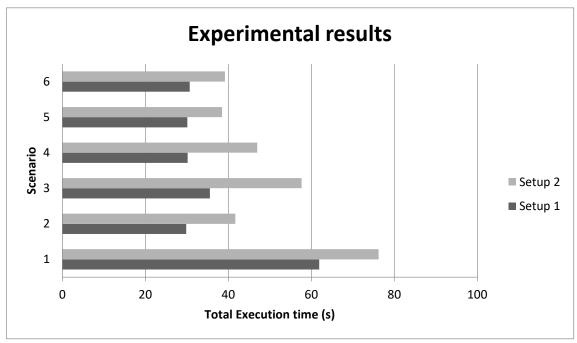

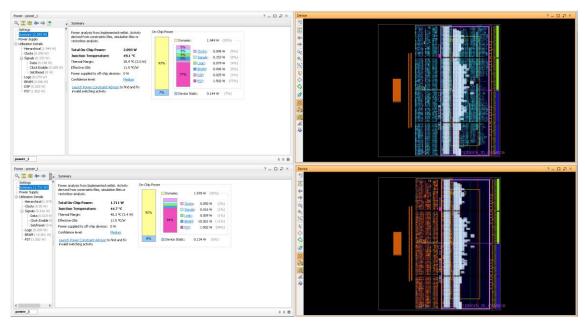

Beyond resource and power savings, partial reconfiguration can help to increase system performance. In most cases, this is achieved by spending more resources for specific accelerator modules. With more area, we can exploit a higher level of parallelism, which in turn permits a faster processing of the accelerator modules. If different accelerators are used sequentially (i.e., different accelerators are executed mutually exclusive in the time domain), we can exploit runtime reconfiguration in order to provide more resources per accelerator.